10Gbpsフルレートでも安定した動作。FPGA化により低消費電力・ダウンサイジングに成功

~VM上で増加し続けるトラフィックを集中的に処理するハードウエアアクセラレータ~

・従来のMany Core Processor搭載品より低消費電力(当社比50%減)

・標準的なNICサイズのPCI Expressカードにダウンサイジング

・FPGA化により広範かつ柔軟な製品展開が可能

株式会社アルチザネットワークス(代表取締役社長:床次隆志/東京都立川市)は、IAサーバのPCIeスロットに搭載することにより、VM上で増加し続けるトラフィックを集中的に処理するハードウエアアクセラレータ「PowerNFV」の開発品を「Interop Tokyo 2016」に出展いたします。従来のMany Core Processorを搭載したアーキテクチャをFPGA化することにより、低消費電力(当社比50%減)、ダウンサイジングを実現しPCI Expressの標準的なカードとしての使用が可能となる見込みです。

本年より、仮想化アクセラレータとしてPowerNFVの評価を協業先にて行っております。カード折り返し、VM折り返しでの性能、スループット、安定性テストで高い評価を頂いております。Interop Tokyo 2016では、通常のIPパケット、VxLANカプセル化パケットを、カード折り返し、VM折り返し、ミラーリング、統計情報表示の実機によるデモを実施します。

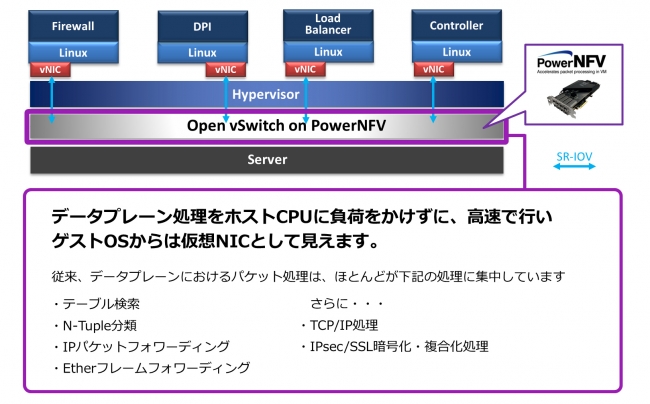

PowerNFV Open vSwitchでの活用例

PowerNFV Open vSwitchでの活用例

<開発の背景>

ユーザートラフィックの増加は今後も加速するものと予測されています。一方、IA(Intel® Architecture)サーバ上で動作するCPUのクロック周波数の向上はほぼ限界に達してきており、VMを処理するサーバのCPUはこれまで以上にデータプレーンの処理に多くのリソースを占有されることになります。特にIPパケットのフォワーディングに必要なフローテーブルの検索がボトルネックとなる傾向にあります。ホストCPUがデータプレーン処理に集中するあまり、コントロールプレーンの処理が疎かになる、という問題をサーバの追加導入のみで解決することは困難です。この問題を解決することを目的にPowerNFVを開発しています。

もうひとつ、仮想化において大きな課題となるのが障害の検知と切り分けです。不測の事態への備えとして、効率的なトラフィックデータの監視、迅速なトラブルシュート、証拠保全も運用時には必要となります。PowerNFVではホストCPUに負荷を与えずに各VMの死活監視、性能監視を行うことができます。ホストCPUを使用してこれを行うことは可能ですが、この処理を行うためにホストCPUにさらなる負荷をかけることは本末転倒です。PowerNFVはマルチベンダーのアプリケーションの性能状態を分かりやすく把握するため、さまざまなグループでの稼働状態や負荷状況の表示や、ダッシュボード画面による一覧表示、詳細なリソース変動を把握するためのグラフ表示機能を提供します。この機能により、仮想サーバ、物理サーバで構成されたNFVインフラの性能状況を表示することができ、迅速な問題の切り分け、万が一の場合の証拠保全までが可能となります。

<今後の展望>

アルチザネットワークスは「通信テスター開発」という従来の事業ドメインを「通信インフラ機器開発支援」へと拡張し、「PowerNFV」を、NFV導入の効果を最大化していくためのソリューションとして、2017年末以降に商用ネットワークに採用されることを目指して開発を進めています。今後もトラフィックが予想を上回り増え続ける環境においても、NFVの本来の目的であるCAPEX/OPEXを低減しながら、柔軟かつ堅牢性の高いインフラの構築を実現するために、本分野での積極的な製品開発を行ってまいります。

このプレスリリースには、メディア関係者向けの情報があります

メディアユーザー登録を行うと、企業担当者の連絡先や、イベント・記者会見の情報など様々な特記情報を閲覧できます。※内容はプレスリリースにより異なります。

すべての画像

- 種類

- 商品サービス

- ビジネスカテゴリ

- ネットワーク・ネットワーク機器アプリケーション・セキュリティ

- ダウンロード