SFN、工場における半導体生産の速度を10倍、純利益を40~50倍向上させる「インフラストラクチャ・タイムマシン」を発表

Zpolar® Tunnel Logic (ZTL)搭載のZpolar トランジスタ製造向けBizen® ウェハ・プロセスにより、台湾と韓国の半導体メーカーの独占に終止符を打ち、半導体不足問題を解決

Bizenのウェハ・プロセス、Zpolarトランジスタ、Zpolar Tunnel Logic(ZTL)を複合的に組み合わせたソリューションを開発しているSearch for the Next(SFN)は旧型の180nmや1㎛のジオメトリの工場でも最先端の工場で生産されるCMOSデバイスと同等の性能を持つICチップの設計と生産を可能にするプロセス・ノードとして4つのITM(インフラストラクチャ・タイムマシン)ファミリを発表しました。たとえば、海外企業への売却をめぐって政治的、経済的な争点となっている英国最大の半導体製造工場、Newport Wafer Fabをはじめとする180nmフォトリソグラフィック・ステッパを備えた工場がITM35を実装すれば、35nm CMOSのパフォーマンス(サイズ、スピード、性能)を持つZTLデバイスを生産できるようになります。

SFNのCEOのDavid Summerlandは「これまで、Zpolarトランジスタ、ZTLロジック、5GやRISC-Vなどのアプリケーション向け高性能チップの生産は世界の高性能半導体の生産を支配する台湾の半導体メーカー大手、TSMCなどの工場に限られていました。今後は英国やその他の欧米諸国の工場が競争力を取り戻すだけでなく、台湾や韓国の大手メーカーを追い抜き、国益も守ることが可能になります」と述べました。

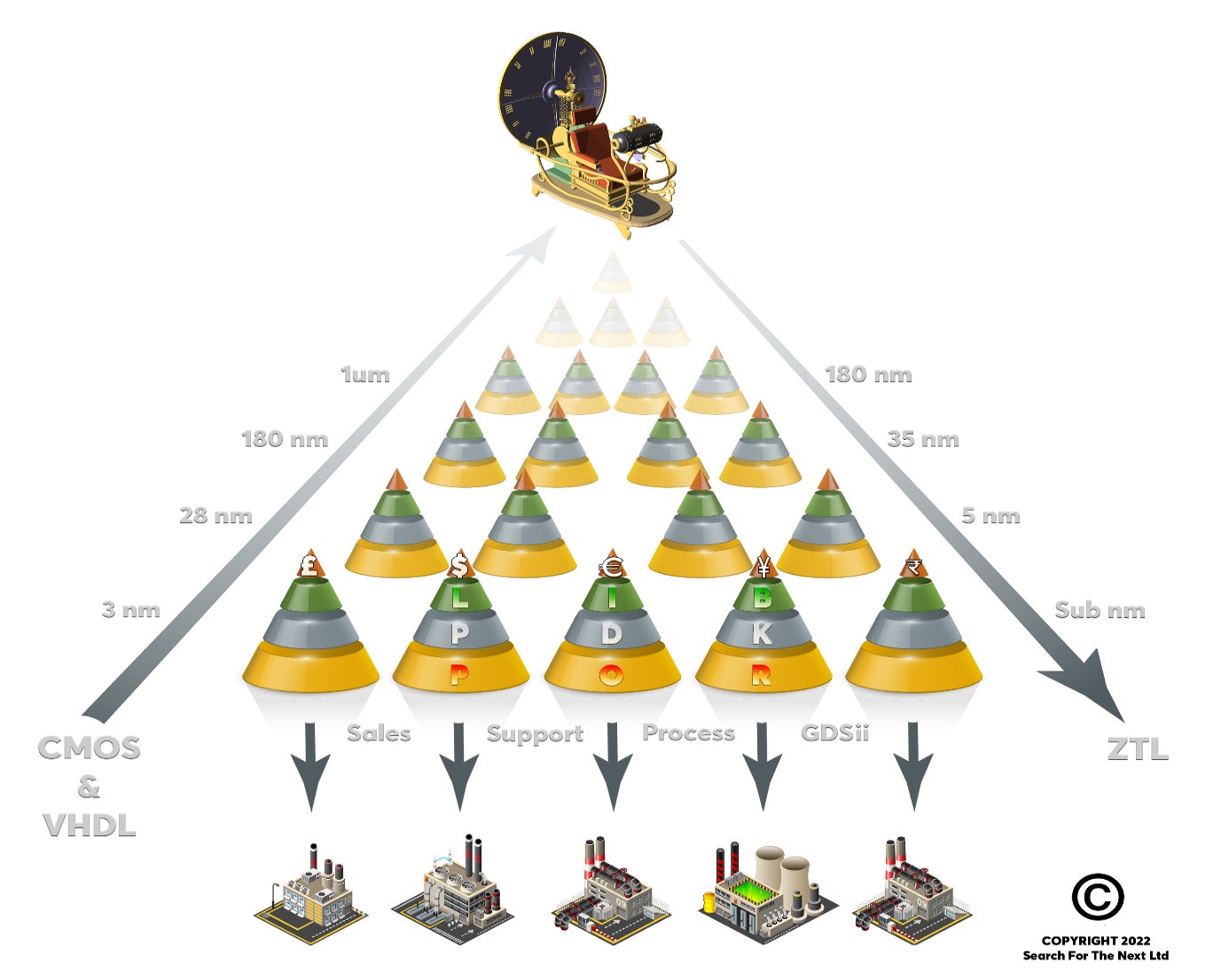

今回、SFNは1μm相当で180nm CMOSの性能を持つZTLチップの製造を可能にする「ITM180」、180nmプロセス・ノードの工場で35nm CMOS相当のICを製造可能にする「ITM35」、28nmステッパで5nm CMOSの性能を実現する「ITM5」、そして最先端の3nm工場でなんとサブnmレベルのオングストローム・プロセスを可能にする「ITMSubnm」の4種類のITMをリリースします。お選びいただいたITMにはVHDLが組み込まれ、最終的なIC用のPOR(プロセス・オブ・リファレンス)とGDSiiの両方が提供されます。インフォグラフィックのプロセスは次の通りです。

------------------------------------------------------------

Bizenには量子力学を応用したウェハ・プロセス技術が投入されています。Bizen ZTLチップは必要なプロセス・レイヤー数を大幅に減少し、世界の大型ジオメトリ工場における複雑なデバイスの生産を可能にします。Summerlandは「180nmの工場がITM35を導入して35nm CMOS相当の性能を持つZTLチップを生産する場合、実際の35nm CMOSプロセスよりも10倍高速になり、生産時間が1/10で済みます。純利益に換算すると、Bizen向けに改装した工場は40~50倍に増加します。同時に、現在の半導体不足の解消にも大きく貢献します」と説明しています。

Bizenのプロセスは新しい技術ですが、標準CMOSプロセス機器を使用した標準的なシリコン・プロセス技術で稼働できます。Bizenは英国の工場で4年かけて開発し、SFNが「最高水準」のテスト・ウェハを作り出し、特性化しました。抽出した特性データはJMPデータブックに掲載され、Cadence設計環境で動作するSPICEモデルの構築に使用されており、Synopsisウェハ・プロセス・フローの結果にもマッチしています。

最後に、Summerlandは「CMOS技術のロードマップは少なくとも2036年まで有効で、デバイス・ジオメトリを2オングストロームまで微細化できると考えられます。CMOSはロジックであり、MOSはトランジスタであることを理解することが重要です。CFETSもスタック構造のnMOSとpMOSです。Bizen/ZTLは非常に大きな躍進であり、他の複雑なアプローチを無用にします。Zpolarトランジスタにより、無極性構造のCMOSへの依存から脱却し、Zpolarならではの敏捷性の高い入力と最小限の垂直サイズという利点を活かすことができます。『タイムマシン』という名称はBizenウェハ・プロセス、Zpolarトランジスタ、Zpolar Tunnel Logic(ZTL)の複合的な組み合わせの特徴を的確に示していると思います。この技術を使えば、IC設計者は製造能力面で10年前の設備でZTLデバイスを作成し、現在あるいは未来の性能さえ実現できるからです。ICの製造プロセスが以前よりはるかにシンプルになり、ウェハあたりのチップ生産数が増えるため、半導体不足を解消することができ、外国企業に依存したりそのロードマップをたどったりする必要がなくなります。我々が今行こうとしているのはロードマップを必要としません」と述べました。

Bizenは特許で保護されており、英国でSearch for the Next(SFN)によって開発されました。

Bizen、ZTL、SFNについて、詳しくは https://www.wafertrain.com/blog をご覧いただくか、 https://www.wafertrain.com/discussions の議論にご参加ください。以下のソーシャルメディアでも情報を掲載しています。

https://www.linkedin.com/company/wafertrain

https://twitter.com/wafertrain

https://www.facebook.com/wafertrain/

https://www.instagram.com/wafertrain/

Bizen - それはメーカーの夢である

SFNについて

2017年にノッティンガム大学ビジネスパークのインジェヌイティ・ビルで設立されたSearch for the Next(SFN)はBizenウェハ・プロセス、Zpolarトランジスタ、Zpolar Tunnel Logic(ZTL)の複合的な組み合わせを開発し、工場における生産速度を10倍に、純利益を約40~50倍向上させています。このプロセスはファウンドリーでも実証され、その後数年にわたってテスト、特性化、ロギングが行われてきました。SFNではそれを「インフラストラクチャ・タイムマシン(ITM)」と呼んでいます。

この技術は特許によって保護されており、SFNが100%出資する工場で本格稼働しながら開発されています。SFNには広範な層の個人投資家が投資しており、その株式評価額はすでに市場外取引で1億米ドルに達しています。

SFNとBizenについて、詳しくは以下にお問い合わせください。

今回、SFNは1μm相当で180nm CMOSの性能を持つZTLチップの製造を可能にする「ITM180」、180nmプロセス・ノードの工場で35nm CMOS相当のICを製造可能にする「ITM35」、28nmステッパで5nm CMOSの性能を実現する「ITM5」、そして最先端の3nm工場でなんとサブnmレベルのオングストローム・プロセスを可能にする「ITMSubnm」の4種類のITMをリリースします。お選びいただいたITMにはVHDLが組み込まれ、最終的なIC用のPOR(プロセス・オブ・リファレンス)とGDSiiの両方が提供されます。インフォグラフィックのプロセスは次の通りです。

インフォグラフィック:Bizenインフラストラクチャ・タイムマシン(ITM)

インフォグラフィック:Bizenインフラストラクチャ・タイムマシン(ITM)

------------------------------------------------------------

Bizenには量子力学を応用したウェハ・プロセス技術が投入されています。Bizen ZTLチップは必要なプロセス・レイヤー数を大幅に減少し、世界の大型ジオメトリ工場における複雑なデバイスの生産を可能にします。Summerlandは「180nmの工場がITM35を導入して35nm CMOS相当の性能を持つZTLチップを生産する場合、実際の35nm CMOSプロセスよりも10倍高速になり、生産時間が1/10で済みます。純利益に換算すると、Bizen向けに改装した工場は40~50倍に増加します。同時に、現在の半導体不足の解消にも大きく貢献します」と説明しています。

Bizenのプロセスは新しい技術ですが、標準CMOSプロセス機器を使用した標準的なシリコン・プロセス技術で稼働できます。Bizenは英国の工場で4年かけて開発し、SFNが「最高水準」のテスト・ウェハを作り出し、特性化しました。抽出した特性データはJMPデータブックに掲載され、Cadence設計環境で動作するSPICEモデルの構築に使用されており、Synopsisウェハ・プロセス・フローの結果にもマッチしています。

最後に、Summerlandは「CMOS技術のロードマップは少なくとも2036年まで有効で、デバイス・ジオメトリを2オングストロームまで微細化できると考えられます。CMOSはロジックであり、MOSはトランジスタであることを理解することが重要です。CFETSもスタック構造のnMOSとpMOSです。Bizen/ZTLは非常に大きな躍進であり、他の複雑なアプローチを無用にします。Zpolarトランジスタにより、無極性構造のCMOSへの依存から脱却し、Zpolarならではの敏捷性の高い入力と最小限の垂直サイズという利点を活かすことができます。『タイムマシン』という名称はBizenウェハ・プロセス、Zpolarトランジスタ、Zpolar Tunnel Logic(ZTL)の複合的な組み合わせの特徴を的確に示していると思います。この技術を使えば、IC設計者は製造能力面で10年前の設備でZTLデバイスを作成し、現在あるいは未来の性能さえ実現できるからです。ICの製造プロセスが以前よりはるかにシンプルになり、ウェハあたりのチップ生産数が増えるため、半導体不足を解消することができ、外国企業に依存したりそのロードマップをたどったりする必要がなくなります。我々が今行こうとしているのはロードマップを必要としません」と述べました。

Bizenは特許で保護されており、英国でSearch for the Next(SFN)によって開発されました。

Bizen、ZTL、SFNについて、詳しくは https://www.wafertrain.com/blog をご覧いただくか、 https://www.wafertrain.com/discussions の議論にご参加ください。以下のソーシャルメディアでも情報を掲載しています。

https://www.linkedin.com/company/wafertrain

https://twitter.com/wafertrain

https://www.facebook.com/wafertrain/

https://www.instagram.com/wafertrain/

Bizen - それはメーカーの夢である

SFNについて

2017年にノッティンガム大学ビジネスパークのインジェヌイティ・ビルで設立されたSearch for the Next(SFN)はBizenウェハ・プロセス、Zpolarトランジスタ、Zpolar Tunnel Logic(ZTL)の複合的な組み合わせを開発し、工場における生産速度を10倍に、純利益を約40~50倍向上させています。このプロセスはファウンドリーでも実証され、その後数年にわたってテスト、特性化、ロギングが行われてきました。SFNではそれを「インフラストラクチャ・タイムマシン(ITM)」と呼んでいます。

この技術は特許によって保護されており、SFNが100%出資する工場で本格稼働しながら開発されています。SFNには広範な層の個人投資家が投資しており、その株式評価額はすでに市場外取引で1億米ドルに達しています。

SFNとBizenについて、詳しくは以下にお問い合わせください。

このプレスリリースには、メディア関係者向けの情報があります

メディアユーザーログイン既に登録済みの方はこちら

メディアユーザー登録を行うと、企業担当者の連絡先や、イベント・記者会見の情報など様々な特記情報を閲覧できます。※内容はプレスリリースにより異なります。

すべての画像

- 種類

- 商品サービス

- ビジネスカテゴリ

- 電子部品・半導体・電気機器

- ダウンロード