アルテラ、28nm製品ポートフォリオの全容を発表、多様なニーズに最適な選択肢を提供

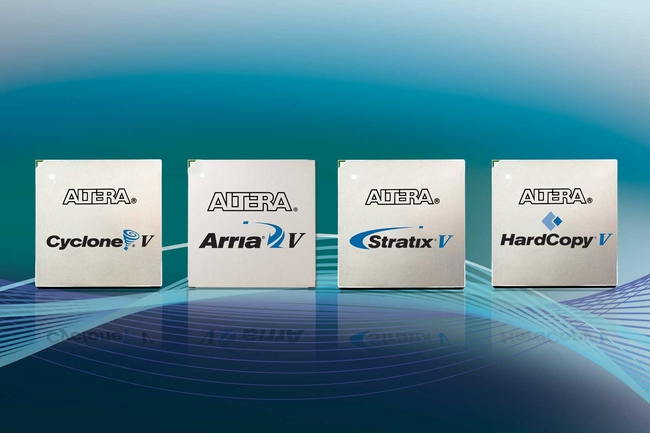

プログラマブル・ロジック・ソリューションの世界的リーディング・カンパニーであるアルテラ・コーポレーション (本社:米国カリフォルニア州サンノゼ、社長兼 CEO:ジョン・デイナ、日本法人:東京都新宿区、代表取締役社長:日隈寛和、NASDAQ:ALTR 以下、アルテラ)は、米国時間1月24日(日本時間:1月25日)、同社の28nm製品ポートフォリオを発表しました。アルテラの28nm製品ポートフォリオは、新製品Cyclone(サイクロン)® V(ファイブ)FPGAファミリおよび Arria(アリア)® V(ファイブ) FPGAファミリと、最近拡張されたStratix(ストラティクス)® V(ファイブ) FPGAファミリ、そして発表済みのHardCopy(ハードコピー)® V(ファイブ) ASICファミリで構成され、明確に差別化されたソリューションを提供し、顧客の多様なデザイン・ニーズに応える、業界で最も包括的なデバイス・オプションを提供します。

アルテラは長年にわたる業界を代表する顧客企業との密接な協力関係を通じて、最大のバンド幅から最小の消費電力まで、顧客の多彩なアプリケーションに求められる性能、機能、消費電力の要件を深く理解しています。アルテラは、トランシーバ技術、アーキテクチャ、IP統合、およびプロセス技術における自社の優位性を活かし、28nm製品ポートフォリオによって、顧客の多様な設計課題に応える最適なソリューションの選択肢を提供します。

・トランシーバ技術: アルテラは、業界をリードする自社の実証済みトランシーバ技術を各28nmデバイス・ファミリの性能範囲に合わせて最適化しています。アルテラの28nmデバイスは、600Mbpsから28Gbpsまでのトランシーバ性能をサポートします。

・アーキテクチャ: 性能および効率に最適化されたオンチップ・メモリ; 必要なアプリケーションバンド幅、消費電力およびコスト要件をサポートするハードおよびソフト・メモリ・コントローラ; 各性能に最適化されたハイエンド、ミッドレンジ、および低コストI/O

・IP統合: アルテラは、顧客のコスト、消費電力、および性能要件に対応するために、PCI Express®(PCIe®) Gen2 x 1 / x4、PCIe Gen3 x 8、Interlaken、および100ギガビット・イーサネット(100GbE)などのさまざまなシステム・レベルIPをハード化しています。

・プロセス技術: 多種多様なアプリケーションに効果的に対応するために、アルテラは、ハイエンド製品ファミリ(Stratix V FPGA)およびHardCopy V ASICにはTSMCの28nm High Performance(28HP)プロセス技術を採用し、低コスト(Cyclone V FPGA)およびミッドレンジ(Arria V FPGA)製品ファミリには、TSMCの28nm Low-Power(28LP)プロセス技術を採用しています。コスト、性能、および消費電力の最適なバランスには28LPプロセスが必要であり、ハイエンド・アプリケーションに求められるコアおよびトランシーバ性能には28HPプロセスが不可欠です。

新製品となるCyclone V FPGAファミリは、低消費電力とボード面積が課題となるモーターコントロールやディスプレイ、ソフトウェア無線(software-defined radio)などのアプリケーションに最適です。Cyclone Vファミリは、前世代品に比べて40%低いトータル消費電力、最大5Gbpsで動作する12個のトランシーバ、ハード化されたPCIe Gen2 x 1ブロック、およびLPDDR2、Mobile DDR、およびDDR3外部メモリをサポートするハード・メモリ・コントローラを備えています。Cyclone Vファミリの詳細は、www.altera.co.jp/cyclonevをご覧下さい。

また、アルテラは、リモート無線ユニット、映像スタジオ・ミキサ、10G/40Gラインカードなど、バランスの取れたコスト、低消費電力、および高性能を必要とするターゲット・アプリケーション向けに開発されたArria V FPGAファミリを明らかにしました。トータル消費電力が前世代に比べて40%少ないArria V FPGAファミリ・デバイスは、最大10Gbpsで動作するトランシーバ、DDR3外部メモリをサポートするハード・メモリ・コントローラ、および可変精度DSPブロックによる効率的なシストリック FIR(systolic finite impulse response)フィルタを備えています。Arria Vファミリの詳細は、www.altera.co.jp/arriavをご覧下さい。

Stratix V FPGAファミリは、40G/100Gラインカード、先進的なLTE基地局、ハイエンドRFカード、軍用レーダーなど、広範な高帯域幅アプリケーションに対応しています。アルテラは、進化する市場ニーズに対応するために、Stratix Vファミリの機能を拡張しました。Stratix V GX FPGAにおける最大トランシーバ・データ速度は14.1Gbpsに高められ、16G Fibre Channel などの新しい高速プロトコルをサポートします。また、Stratix V GX FPGAの集積度は、モノリシック・ダイで110万相当ロジック・エレメント(LE)にまで高められたことで、より高いレベルのシステム統合を可能にします。Stratix Vファミリの詳細は、www.altera.co.jp/stratixvをご覧下さい。

HardCopy V ASICは、低NRE(Nonrecurring-Engineering)、低リスク・トランシーバ内蔵ASICにおけるアルテラの優位性を拡充します。HardCopy V ASICは、前世代のHardCopy ASICデバイスと比べて、トランシーバ、I/O、およびコアロジックにより高い性能を提供し、より高度なロジックおよびメモリ統合を可能にします。これらの新しい機能により、HardCopy V ASICは、低消費電力、低コスト、あるいは稼働時により高いレベルのSEU(Single-Event Upset)耐性を必要とする幅広い量産アプリケーションをサポートできるようになりました。

デザイン生産性の向上を求める顧客のニーズに対応すべく、アルテラの28nm製品ポートフォリオは、CPLD、FPGA、およびHardCopy ASICデザインの性能および生産性においてプログラマブル・ロジック業界で最も優れたソフトウェアであるアルテラのQuartus® II 開発ソフトウェアによってサポートされます。Quartus II ソフトウェアの新しいシステム・レベル・インテグレーション・ツールQsysは、IP統合を簡素化し、ハード化されたARM® Cortex™-A9 MPCore™など、業界で最も広範なエンベデッド・プロセッサの選択肢を提供します。

アルテラ プロダクト&コーポレート・マーケティング担当バイスプレジデントのビンス・フー (Vince Hu) は、「すべての顧客デザインは特有であり、その個別の要件を満たす最適な機能と性能を持ち、かつ、顧客アプリケーションの差別化を可能にするソリューションを求めています。アルテラの28nm製品ポートフォリオは、当社のトランシーバ・デザインやシステム・レベルIP、デザイン・ツール、およびTSMC社とのプロセス最適化などの重要な領域における継続的な投資を活かして、業界で最も広範なソリューション群を提供します」と述べています。

アルテラの28nm製品群の詳細情報は、www.altera.co.jp/28nmportfolioをご覧下さい。

【アルテラ・コーポレーションについて】

アルテラ・コーポレーションは、プログラマブル・ロジック・ソリューションの世界的リーディング・カンパニーです。1983年にシリコンバレーで創業した世界で最初のファブレス企業であり、1988年に NASDAQ に上場しました。FPGA / CPLD、ASICなど、カスタム・ロジックの分野におけるテクノロジー・リーダーとして高成長を続け、顧客企業のイノベーションに貢献しています。世界各国に拠点を持ち、日本法人である日本アルテラ株式会社は1990年に設立されました。顧客志向のソリューションが高く評価され、日本における PLD 市場でトップシェアを維持しています。アルテラのFPGA、CPLD、およびASICデバイスついての詳細情報は、アルテラのウェブサイト(www.altera.co.jp)をご覧ください。Facebook、RSS、Twitterでも情報提供を行っています。

・Altera、The Programmable Solutions Company、アルテラのロゴ、弊社特定デバイスの定義、およびその他の商標ならびにサービス・マークを意味する語彙は、特記されていない限り、すべてアルテラ・コーポレーションの米国及びその他の国における登録商標、商標または サービス・マークです。その他記載されている製品名あるいはサービス名は、http://www.altera.com/legalに記載されている各所有企業に帰属します。

このプレスリリースには、メディア関係者向けの情報があります

メディアユーザーログイン既に登録済みの方はこちら

メディアユーザー登録を行うと、企業担当者の連絡先や、イベント・記者会見の情報など様々な特記情報を閲覧できます。※内容はプレスリリースにより異なります。

すべての画像