アナログインメモリ計算回路の非理想的特性を取り込むODEベース学習手法を開発

―実用規模の学習に成功―

[ 発表者 ]

・酒見 悠介 (千葉工業大学 数理工学研究センター 上席研究員/東京大学国際高等研究所ニューロインテリジェンス国際研究機構(WPI-IRCN) 連携研究者)

・岡本 有司 (京都大学 大学院医学研究科 特定助教)

・森江 隆 (九州工業大学 大学院生命体工学研究科 特任教授・名誉教授)

・信川 創 (千葉工業大学 情報変革科学部 教授)

・細見 岳生 (日本電気株式会社 セキュアシステムプラットフォーム研究所 シニアプロフェッショナル)

・合原 一幸 (東京大学国際高等研究所ニューロインテリジェンス国際研究機構(WPI-IRCN) エグゼクティブ・ディレクター/東京大学 特別教授・名誉教授/千葉工業大学 数理工学研究センター 主席研究員)

キーワード:アナログインメモリ計算、アナログ回路、物理モデル、スパイキングニューラルネットワーク、エッジAI

[ 概要 ]

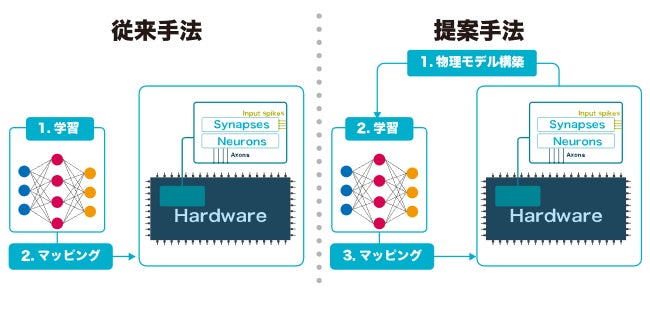

酒見悠介、岡本有司、森江隆、信川創、細見岳生、合原一幸による研究チームは、超低消費電力でAI推論が可能な次世代ハードウェアであるアナログインメモリ計算を効率的に動作させる新しい学習手法の開発に成功しました。この学習手法の肝は、アナログハードウェアの動作を常微分方程式(ordinary differential equation: ODE)で記述し、それを直接学習させることにあります。これにより、従来は学習アルゴリズムの中に取り込めなかったアナログ回路特有の複雑な非線形特性を取り込むことができます。しかし、この物理モデルの学習は計算負荷が高く実用的な規模の学習モデルを学習させることができませんでした。そこで、本研究では、differentiable spike-time discretization (DSTD)とよぶ新しい学習手法を開発し、学習効率を1000倍程度高めることで実用規模とされる8層の畳み込みニューラルネットワークの学習に成功しました。学習の結果、従来は学習性能を低減させるため、「非理想的」と考えられていた実際のアナログ回路の複雑性が、むしろ学習性能を高める場合も確認できました。さらに、回路設計とそのシミュレーションも実施し、実回路での同手法の有効性の検証も行いました。本手法は、従来は回避すべき存在であったアナログ回路の非理想的特性を活用することができるため、アナログインメモリ計算回路の設計常識を大きく覆す可能性があります。この成果は、2025年8月18日に査読付き国際学術雑誌「Advanced Intelligent Systems」で公開されました。

詳細は千葉工業大学プレスリリースをご覧ください。

このプレスリリースには、メディア関係者向けの情報があります

メディアユーザー登録を行うと、企業担当者の連絡先や、イベント・記者会見の情報など様々な特記情報を閲覧できます。※内容はプレスリリースにより異なります。

すべての画像