ザイリンクス、革新的なアダプティブ コンピューティング製品カテゴリを発表

ACAP イメージ図

ACAP イメージ図

ザイリンクスの社長兼最高経営責任者 (CEO) であるビクター ペン (Victor Peng) は、「ACAP は、業界に破壊的なインパクトを与える大きな技術革新であり、ザイリンクスにとって FPGA の発明以来の金字塔となります。この革新的なアーキテクチャは、ザイリンクスが FPGA の企業、ハードウェア開発者のみを支援する企業からの脱却を目指す上で、重要な企業戦略の柱となります。データ センターをはじめとする幅広い市場に ACAP 製品が導入されることで、適応性のあるアクセラレーテッド コンピューティングの普及が進み、インテリジェント、コネクテッドかつアダプティブな世界がより早く現実になるでしょう」と述べている。

ACAP 技術の詳細

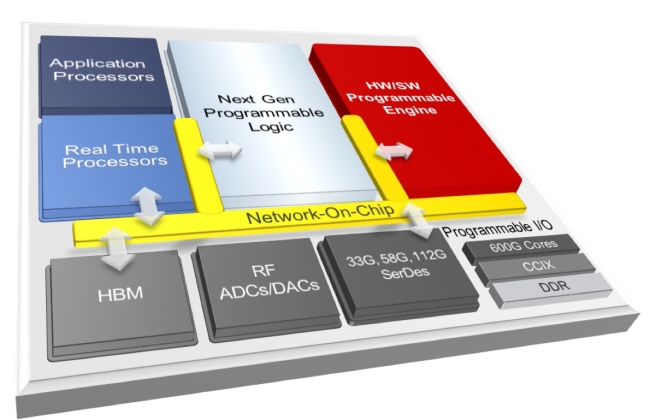

ACAP の中核にあるのは、分散メモリおよびハードウェア プログラマブルな DSP ブロックを含む次世代 FPGA ファブリック、マルチコア SoC、そして、ソフトウェア プログラマブルでありながらハードウェアとして適応性がある 1 つまたは複数の演算エンジンである。これらがネットワーク オン チップ (NoC) で接続されている。ACAP のその他の構成要素としては、高度に統合されたプログラマブル I/O 機能、統合されたハードウェア プログラマブルなメモリ コントローラーからの測距機能、高度な高速シリアル トランシーバ技術がある。さらに、高帯域幅メモリ (HBM) を統合した最先端の RF-ADC および DAC を搭載するデバイスもある。

ソフトウェア開発者は、C/C++、OpenCL、Python などのツールを使用して ACAP ベースのシステムを開発できる。FPGA 用ツールを使用して RTL レベルで ACAP をプログラムすることも可能である。

Moor Insights & Strategy 社の創設者である パトリック ムーアヘッド (Patrick Moorhead) 氏は、「ACAP はコンピューティングの未来を表すものです。ACAP により、従来、数日をかけて行っていたゲノム解析を 2 ~ 3 分で行うことが可能になります。また、データ センターにおいては、日中にビデオ トランスコーディング処理を行わせ、夜間には画像認識を行わせるなど、計算要求によってサーバーのワークロードを変更するようにプログラムすることが可能になります。これは極めて重要です」と述べている。

ACAP の開発期間は 4 年、累積研究開発費は 10 億米ドルを超える。現在、「ACAP および Everest」の開発にはザイリンクスのハードウェアおよびソフトウェア技術者 1,500 人以上が従事している。ソフトウェア ツールは、既に主要な顧客に提供されている。「Everest」は 2018 年にテープ アウトされ、2019 年に顧客向けに出荷予定である。

「EVEREST」による性能の向上

「Everest」にディープ ニューラル ネットワークを実装した場合、現在最新の 16nm Virtex® VU9P FPGA と比べて 20 倍の性能向上が期待される。「Everest」を使用した 5G リモート ラジオ ヘッド (RRH) は、最新の 16nm ベースの無線と比較して 4 倍の帯域幅を備える。オートモーティブ市場、インダストリアル市場、科学および医療市場、航空宇宙および防衛市場、試験市場、計測およびエミュレーション市場、オーディオ / ビデオおよび放送市場、さらには民生市場など、多数の市場を横断する幅広いアプリケーションにおいて、性能および電力効率の大幅な向上が見込まれる。

ACAP および「Everest」プロジェクトは本日、ザイリンクスの未来を描いたビクター ペンのビジョンの一環として発表された ( https://japan.xilinx.com/news/press/2018/xilinx-ceo-outlines-new-vision-and-strategy.html )。詳しい情報は、ウェブサイト japan.xilinx.com で公開している。Twitter : @XilinxJapan、Facebook : facebook.com/XilinxInc、LinkedIn : linkedin.com/company/Xilinx をフォローすると、最新情報をチェックできる。

ザイリンクスについて

ザイリンクスは、エンドポイントから、エッジ、クラウドに至るまで、多種多様なテクノロジで迅速なイノベーションを可能にする、極めて柔軟なアダプティブ プロセッサおよびプラットフォームを開発している。ザイリンクスが発明したテクノロジには、FPGA、ハードウェア プログラマブル SoC、ACAP などがある。ザイリンクスは、インテリジェント、コネクテッドかつアダプティブな未来の世界を実現するため、業界で最もダイナミックなプロセッサ テクノロジを提供する。詳しい情報は、ウェブサイト japan.xilinx.com で公開している。

※ザイリンクスの名称およびロゴ、Artix、ISE、Kintex、Spartan、Virtex、Vivado、Zynq、その他本プレスリリースに記載のブランド名は米国およびその他各国のザイリンクスの登録商標または商標です。その他すべての名称は、それぞれの所有者に帰属します。

■下記のザイリンクス株式会社ウェブサイトもご参照ください。

・トップページ : http://japan.xilinx.com/

・プレスリリース (日本語) : https://japan.xilinx.com/news/press.html

・このリリースの全文は次の URL を参照のこと :

https://japan.xilinx.com/news/press/2018/xilinx-unveils-adaptive-compute-acceleration-platform.html

このプレスリリースには、メディア関係者向けの情報があります

メディアユーザーログイン既に登録済みの方はこちら

メディアユーザー登録を行うと、企業担当者の連絡先や、イベント・記者会見の情報など様々な特記情報を閲覧できます。※内容はプレスリリースにより異なります。

すべての画像

- 種類

- 商品サービス

- ビジネスカテゴリ

- 電子部品・半導体・電気機器サーバ・周辺機器

- ダウンロード