アプライド マテリアルズ オングストローム時代の半導体チップ製造向けパターニングソリューションのポートフォリオを拡充

・ 最先端ロジックチップメーカー各社との協業により、Sculpta®パターンシェーピング技術の応用分野を拡大

・ EUVおよび高NA EUVリソグラフィを用いたチップ製造を補完・改善する革新的なエッチング装置とCVDパターニング膜、計測ソリューションを発表

アプライド マテリアルズ(Applied Materials, Inc., Nasdaq:AMAT、本社:米国カリフォルニア州サンタクララ、社長兼CEOゲイリー・E・ディッカーソン)は2月26日(現地時間)、サンノゼで開催中のSPIE Advanced Lithography + Patterningカンファレンスにおいて、「オングストローム時代」のチップパターニング要件に対応する製品とソリューションのポートフォリオを発表しました。半導体メーカーが2nm以降のプロセスノードへの移行を進める中で、EUVや高NA EUVにおけるパターニング課題(配線エッジの粗さ、突き合わせパターン間距離の制約、ブリッジ欠陥、エッジプレースメントエラーなど)への対応が求められており、新たなマテリアルズエンジニアリングや計測技術がますます重要になっています。

勢いに乗るSculpta:導入先と新アプリケーションが拡大

アプライド マテリアルズが昨年のSPIEリソグラフィカンファレンスで発表したCentura® Sculpta®パターニングシステムは、形成されたパターンの先端を伸長加工することで、EUVまたは高NA EUVの1回露光で実現できるよりも突き合わせパターン部を近づけることができます。これによりEUVダブルパターニング工程を削減します。アプライド マテリアルズは現在、あらゆる最先端ロジックチップメーカーと協力して、Sculptaのアプリケーションの数を増やしています。現在アプライド マテリアルズは最先端ロジックチップメーカー各社と協力し、Sculptaのアプリケーションの数を増やしています。パターン間スペーシングの縮小のみならず、たとえばブリッジ欠陥の除去によるパターニングコストとチップ歩留まりの改善などにもSculptaが利用されています。

アプライド マテリアルズのセミコンダクタプロダクトグループ プレジデント、プラブー・ラジャ(Prabu Raja)は次のように述べています。「先進的な半導体メーカーは、Sculptaを生産に導入し、EUVダブルパターニングステップの削減以外の活用方法も模索して、優れた成果を上げています。」「Sculptaはパターニングエンジニアが従来使ってきたツールキットにはない、まったく新しいツールです。技術者が想像力を駆使して困難な問題を新たな方法で解決することで、さらに多くのアプリケーションで使用されるようになるでしょう。」

Intel Corp.のロジックテクノロジー開発担当コーポレートバイスプレジデント、Ryan Russell氏は次のように話しています。「パターンシェーピングは、当社のプロセステクノロジーロードマップ推進に貢献する画期的なソリューションです。当社ではオングストロームプロセスノードにSculptaを採用しており、初期段階ながらスループット改善、ウェーハ歩留まり向上、プロセスの複雑さとコスト低減などの効果が出ています。パターンシェーピングは、高度なパターニングのための新しい戦略を促進し、リソグラフィプリントの限界を押し広げる道を開きます。」

Samsung Electronicsのファウンドリエッチテクノロジーチーム マスター、Jong-Chul Park氏は次のように述べています。「パターンシェーピングは、EUV時代の重要課題に応えるブレークスルー技術です。当社はその早期開発パートナーとして、自社の4nmプロセスでSculptaの評価を進めています。コストや複雑さの低減、歩留まり向上など、好ましい結果が出ることを期待しています」

EUVラインエッジラフネスを修復する新エッチング技術

EUVでは放射される光子数が従来のリソグラフィより少なく、フォトレジスト上のライン/スペースパターンが不鮮明になりがちです。その結果、エッジの粗いラインがウェーハにエッチングされ、チップ回路に断線や短絡が生じる恐れがあります。こうした歩留まりキラー欠陥は、オングストローム時代を迎えて線幅やスペースパターンが狭くなるにつれ、より頻出しやすくなります。

アプライド マテリアルズが本日発表したSym3® Y Magnum™エッチャーは、成膜とエッチングを同一チャンバー内で行う装置です。このユニークなシステムは、粗いエッジに沿って材料を堆積し、EUVラインパターンをウェーハにエッチングする前に平滑化することで、歩留まりの向上とライン抵抗の低減を実現し、チップの性能と消費電力を改善します。ファウンドリ-ロジック分野では、すでに大手半導体メーカーがSym3 Y Magnumを重要なエッチングアプリケーションに採用し、オングストロームノードのEUVパターニングに活用しています。メモリ分野では、Sym3 Y Magnum がDRAMのEUVパターニング用エッチング技術として最も広く採用されています。

オングストローム時代の新たなCVDパターニング膜

アプライド マテリアルズは本日、Producer® XP Pioneer® CVD(化学気相成長)パターニング膜を発表しました。Pioneer膜はフォトレジスト工程の前にウェーハ上に成膜され、所望のパターンを極めて忠実にウェーハに転写するために独自に設計されたフィルムです。Pioneerは、最先端のプロセスノードで使用されるエッチングケミストリに対してより強い独自の高密度カーボン配合をベースとしており、優れた側壁形状の均一性を持つ薄膜スタックを可能にします。Pioneerは、すでに大手メモリメーカーがDRAMのパターニングに採用しています。

Pioneerはアプライド マテリアルズのパターンシェーピング技術Sculptaと協調最適化されており、パターンエンジニアは元のEUVパターンを綿密に制御しながら、パターンを最大限に伸長することができます。Pioneerは新しいエッチング装置Sym3 Y Magnumとも協調最適化され、ロジックやメモリの製造プロセスで重要となるエッチングアプリケーションにおいて、従来のカーボン膜よりも高い選択性と優れた制御性を発揮します。

プレースメントエラーを回避するAseltaテクノロジー

業界をリードするアプライド マテリアルズの電子ビーム計測装置は、世界有数のロジックメーカーやメモリメーカーに採用され、重要なEUVパターニングアプリケーションの開発・制御に力を発揮しています。中でも大きな課題の1つは、各レイヤ上に数十億個もあるフィーチャーを高密度に設定・配置し、次レイヤの対応するフィーチャーと正しく位置合わせすることです。わずかでも配置誤差があるとチップのパフォーマンスや電力消費が悪化し、エラーの程度によっては歩留まりを損なう欠陥につながります。

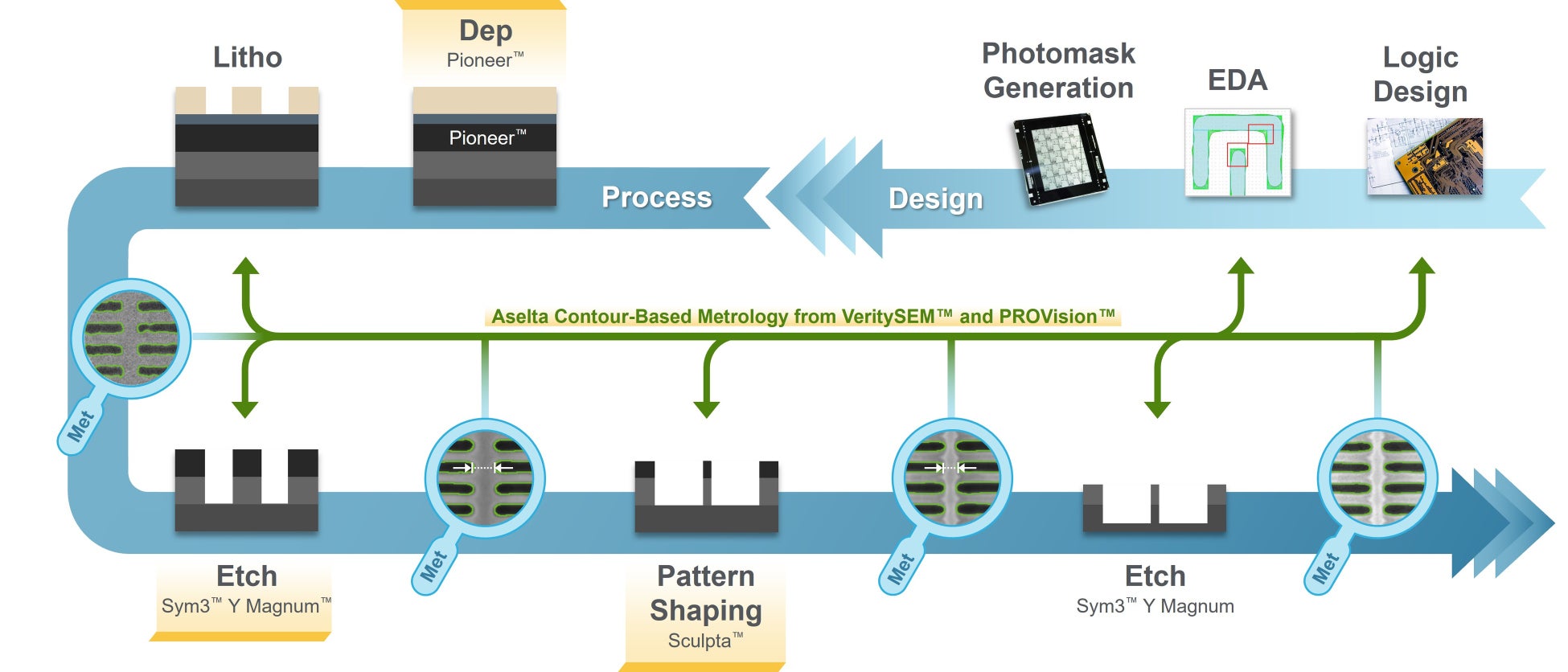

アプライド マテリアルズが先に買収したAselta Nanographicsは、輪郭を利用するデザインベース測定技術のリーダーです。輪郭を利用することで、パターニング技術者はデザインレシピがパターニング膜やウェーハ上に生成する形状についての膨大なデータを得ることができます。このデータをリソグラフィやプロセスフローにフィードバックすれば、より正確なフィーチャーや配置を生成することができます。

アプライド マテリアルズのイメージング&プロセス コントロール担当グループバイスプレジデント、キース・ウェルズ(Keith Wells)は次のように述べています。「Aseltaの輪郭テクノロジーは、当社のCD-SEM計測装置VeritySEM®と電子ビーム計測装置PROVision®にインテグレートされつつあります。これにより半導体メーカー各社は、オングストローム時代の広範な計測課題に応えるユニークかつ包括的な能力を手にすることでしょう」

拡大するパターニング事業と製品ポートフォリオ

アプライド マテリアルズは2012年以来、パターニングを研究開発の優先分野と位置づけ、困難をきわめるパターニング課題の克服に取り組むお客さまを支援すべく、特にEUVや高NA EUVといった新しいアプリケーションを念頭に、斬新な製品やソリューションの提供に力を入れてきました。現在、当社のパターニング製品ポートフォリオには、CVDおよびALD成膜装置、4種の材料除去装置(エッチング、選択的材料除去、パターンシェーピング、CMP)、熱処理プロセス、電子ビーム計測装置が含まれます。当社が参入しているパターニング関連市場は2013年には約15億ドル規模でしたが、2023年には80億ドル以上に成長しているほか、当社の市場シェアは同期間に約10%から30%以上に伸びています。

将来予想に関する記述について

本プレスリリースには、当社の新しい製品と技術から見込まれる恩恵、当社の事業や市場の成長予測とトレンド、業界見通しと需要拡大要因、テクノロジーの遷移など将来の見通しに関する記述や、過去の事実には該当しないその他の記述が含まれています。こうした記述やその前提をなす仮定はリスクや不確定要素に左右され、将来のパフォーマンスを保証するものではありません。こうした記述が明示ないし黙示する帰結と実際の結果の間に大きな違いをもたらし得る要因としては、当社の新しい製品と技術から見込まれる恩恵の不実現;半導体への需要;技術や生産設備に対する取引先企業のニーズ;新たな革新的テクノロジーの導入とテクノロジー移行のタイミング;既存ならびに新開発の製品に対する市場の受容性;当社がテクノロジーに関する知的財産権を取得ならびに保護する能力;適用される法律、規則、規制の遵守を当社が確保する能力;および当社が証券取引委員会(SEC)に提出する書類(最新のForm 10Qおよび8K報告書を含む)に記載しているその他のリスクや不確定要素などがあります。将来の見通しに関する記述はすべて本プレスリリース発表時点における経営陣の推定、予測、仮定に基づくものです。アプライドマテリアルズは将来の見通しに関する記述を更新する義務を負っておりません。

アプライド マテリアルズ(Nasdaq: AMAT)は、マテリアルズ エンジニアリングのソリューションを提供するリーダーとして、世界中のほぼ全ての半導体チップや先進ディスプレイの製造に寄与します。原子レベルのマテリアル制御を産業規模で実現する専門知識により、お客さまが可能性を現実に変えるのを支援します。アプライド マテリアルズはイノベーションを通じてよりよい未来を可能にします。

詳しい情報はホームページwww.appliedmaterials.com でもご覧いただけます。

アプライド マテリアルズ、パターニング ソリューション ポートフォリオを拡大

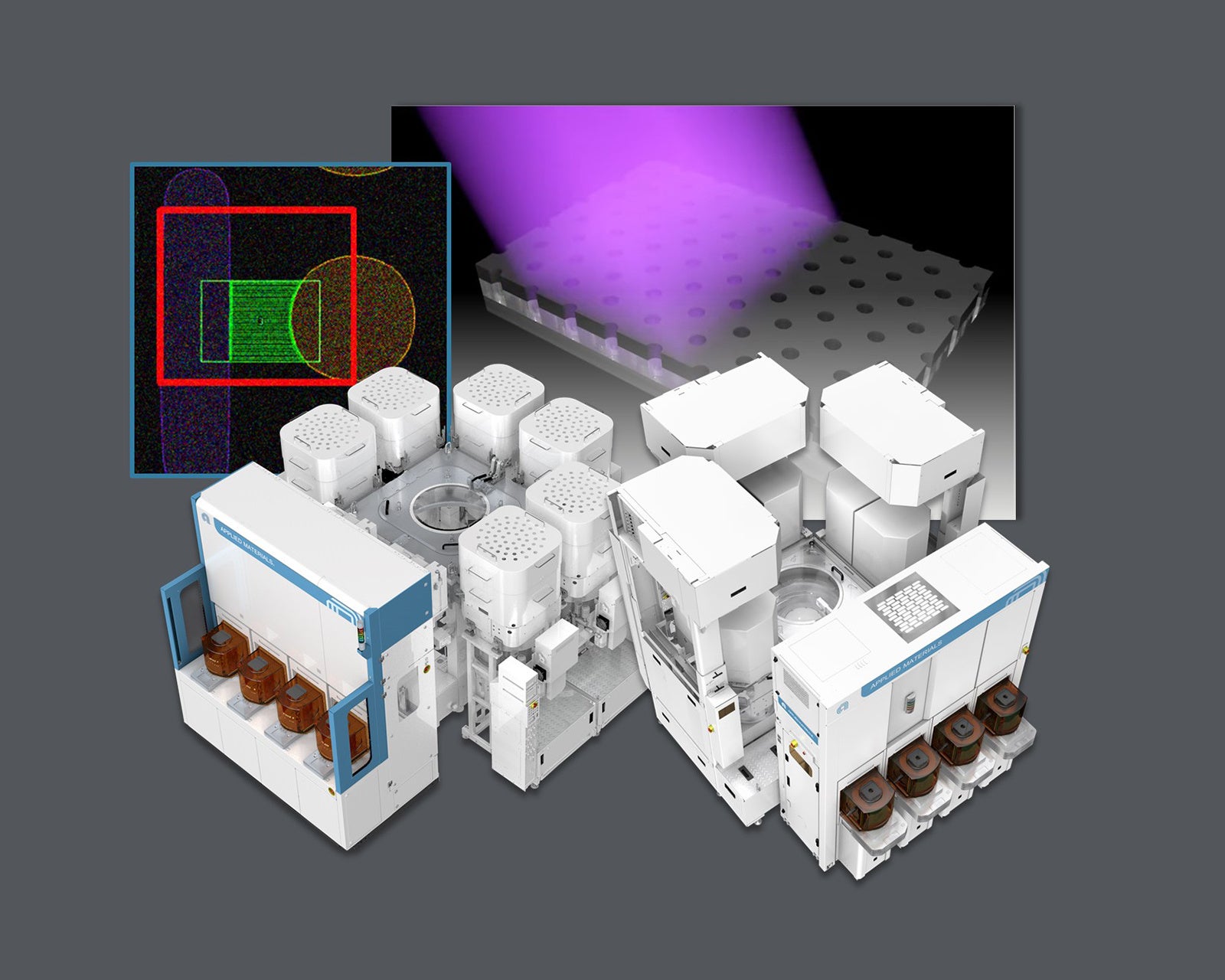

最先端チップのパターニングの課題を克服するために、アプライド マテリアルズは、リソグラフィーの最新技術を補完する技術ポートフォリオを提供します。同社の最新のイノベーションには、Producer® XP Pioneer® CVD パターニング フィルム、Sym3® Y Magnum™ エッチング システム、Centura® Sculpta® パターン形成システム、およびデザインベースの計測用の Aselta 輪郭技術が含まれます。

パターニングエンジニアのツールキットにアプライドマテリアルズがプロセス革新を」をもたらす

今後数年間で、半導体メーカーは、EUV および高 NA EUV リソグラフィーを使用して最小パターンを形成する「オングストローム時代」のチップの実現を目指すでしょう。この高度なパターニングを可能にするには、ソフトウェアと設計ツール、成膜とエッチングの革新、高度な計測と検査システム、パターン形成などのまったく新しいアプローチを含む、エコシステム全体の機能が必要になります。

*************************************************************************

このリリースは2月26日、米国においてアプライド マテリアルズが行った英文プレスリリースをアプライド マテリアルズ ジャパン株式会社が翻訳の上、発表するものです。

アプライド マテリアルズ ジャパン株式会社(本社:東京都、代表取締役社長:中尾 均)は1979年10月に設立。大阪支店、川崎オフィスのほか全国各地にサービスセンターを置き、日本の顧客へのサポート体制を整えています。

このリリースに関するお問い合わせは下記へメールにてご連絡をお願いいたします。

アプライド マテリアルズ ジャパン株式会社 広報宛メール Applied_Materials_Japan@amat.com

ホームページ: www.appliedmaterials.com/ja

すべての画像