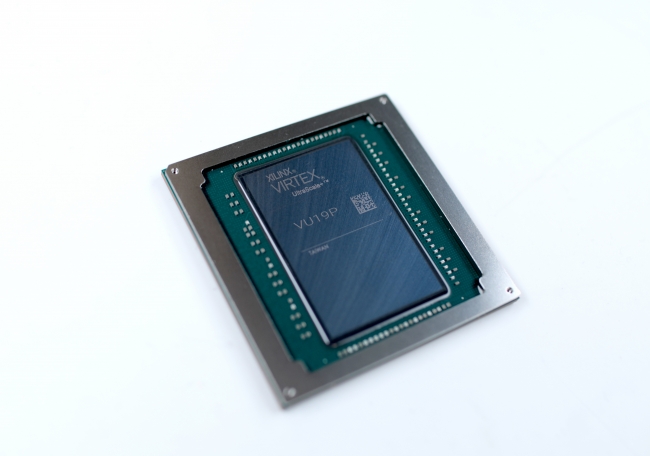

ザイリンクス、世界最大となる900 万個のシステム ロジック セルを搭載したFPGA を発表

irtex UltraScale+ デバイスで、SoC のプロトタイピングやエミュレーションが可能に AI / MLなど最新かつ複雑なアルゴリズム開発を実現

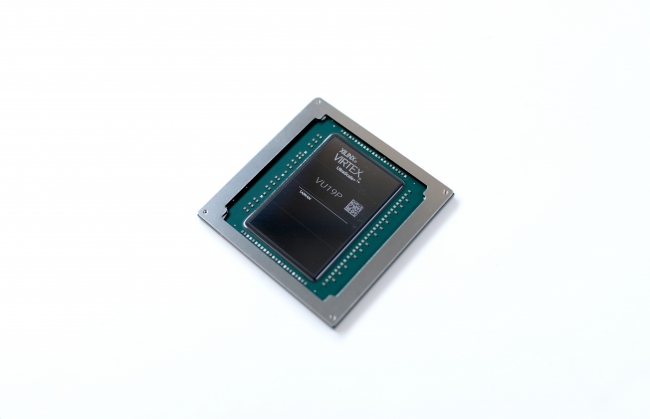

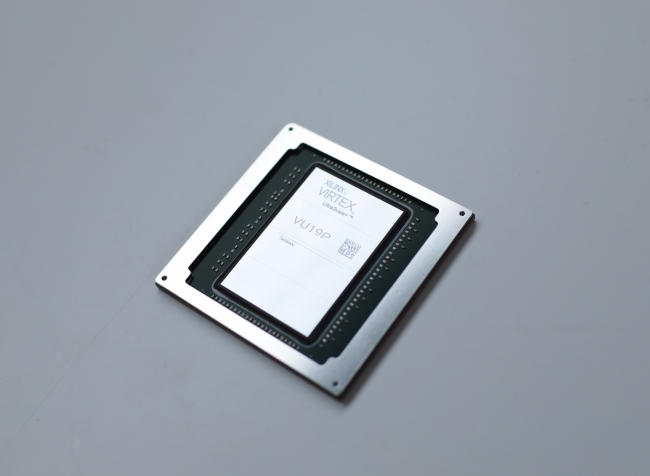

U19P は、900 万個のシステム ロジック セル、最大 1.5 テラビット/秒の DDR4 メモリ帯域幅、最大 4.5 テラビット/秒のトランシーバー帯域幅、および 2,000 以上のユーザー I/O を備えた FPGA として新たな標準を確立する。これにより、今日最も複雑といわれる SoC のプロトタイピングやエミュレーションが可能になり、たとえば人工知能 (AI)、機械学習 (ML)、ビデオ処理、センサー フュージョンに使用される、新しくかつ複雑なアルゴリズムの開発が実現する。VU19P は、これまで業界最大の FPGA であった 20nm Virtex UltraScale 440 FPGA の 1.6 倍の規模を誇る。

プロダクト ライン マーケティングおよびマネージメント担当シニア ディレクター、スーミット・シャー (Sumit Shah) は次のように述べている。

「VU19P を使用することで、ハードウェアの検証時間が短縮されるだけでなく、ASIC または SoC の完成を待たずにソフトウェア開発を開始できます。今回発表するVirtex UltraScale+ VU19Pは、第 1 世代の Virtex-7 2000T、第 2 世代の Virtex UltraScale VU440 に続き、第 3 世代の世界最大の FPGA です。VU19P はシリコン テクノロジだけでは終わらないデバイスで、堅牢かつ実績のあるツール フローおよびそれをサポートする IP も提供されます」

VU19P は、さまざまなデバッグ ツール、可視化ツール、および IP によってサポートされ、次世代のアプリケーションおよびテクノロジを短時間で開発して検証するための包括的な開発プラットフォームを提供する。ハードウェアとソフトウェアの協調検証によって、開発者は物理的なデバイスが利用可能となる前にソフトウェアを起動し、カスタム機能を実装することができる。さらに、ザイリンクスの Vivado® Design Suite を使用すればデザイン フローの協調最適化が可能である。つまり、コストおよびテープアウトのリスクが軽減され、効率が向上して市場投入までの時間が短縮される。

Arm 社のデザイン サービス担当ディレクター、トラン・ニューウェン (Tran Nguyen) 氏は次のように述べている。

「当社の次世代プロセッサ IP および SoC テクノロジの検証プロセスに、ザイリンクスのデバイスはなくてはならないものです。この新しい VU19Pの登場で、Armおよび当社のエコシステム企業は、挑戦的なロードマップ上のテクノロジを迅速に設計、開発、検証できるようになります」

VU19P は、2020 年の秋にリリース予定である。VU19P および Virtex UltraScale+ FPGA 製品ラインの情報は、 japan.xilinx.com/products/silicon-devices/fpga/virtex-ultrascale-plus-vu19p.html で公開している。

ザイリンクスについて

ザイリンクスは、エンドポイントから、エッジ、クラウドに至るまで、多種多様なテクノロジで迅速なイノベーションを可能にする、極めて柔軟なアダプティブ プロセッサおよびプラットフォームを開発している。ザイリンクスが発明したテクノロジには、FPGA、ハードウェア プログラマブル SoC、ACAP などがある。ザイリンクスは、アダプティブ、インテリジェントかつコネクテッドな未来の世界を実現するため、業界で最もダイナミックなプロセッサ テクノロジを提供する。詳しい情報は、ウェブサイト japan.xilinx.com で公開している。

© Copyright 2019 Xilinx, Inc. Xilinx、Xilinx のロゴ、およびこの文書に含まれるその他の指定されたブランドは、米国およびその他各国のザイリンクス社の商標です。

このプレスリリースには、メディア関係者向けの情報があります

メディアユーザーログイン既に登録済みの方はこちら

メディアユーザー登録を行うと、企業担当者の連絡先や、イベント・記者会見の情報など様々な特記情報を閲覧できます。※内容はプレスリリースにより異なります。

すべての画像

- 種類

- 商品サービス

- ビジネスカテゴリ

- 電子部品・半導体・電気機器

- ダウンロード