大規模集積量子コンピューター制御回路のトランジスタが演算性能を低下させる起源を特定

高性能量子コンピューターの実用化に向けて1回の実行あたりの演算回数を増大させる技術の開発に道筋

・極低温では、原子サイズの欠陥に付随する微小な原子位置の乱れが主なノイズ発生起源であることを特定

・ノイズ低減技術の開発、および量子コンピューターの高集積化・高性能化に道筋

概 要

国立研究開発法人 産業技術総合研究所(以下「産総研」という)デバイス技術研究部門 稲葉 工 研究員、岡 博史 研究員、森 貴洋 研究グループ長は、量子ビット素子の制御に用いる極低温下で動作するトランジスタのノイズ発生の起源を特定しました。

量子コンピューターの大規模集積化に向けては、現状では冷凍機外部に設置されている量子ビット素子の制御機能を集積回路化し冷凍機内に設置、極低温で動作させる必要があります。制御用集積回路はノイズに弱いアナログ回路であり、ここで発生するノイズは量子コンピューターの性能を大きく低下させます。これまで、集積回路を構成するトランジスタを極低温下で動作させた場合のノイズ発生の起源は明らかにされていませんでした。今回の研究では、多数のトランジスタについてノイズ発生現象を統計的に評価し、極低温下では原子サイズの欠陥に付随して生じる微小な原子位置の乱れがノイズを発生させることを特定しました。これにより、今後はノイズ低減による制御用集積回路の高性能化、ひいては量子コンピューターの高性能化につながる研究が加速します。

なお、この技術の詳細は、2023年6月15日(日本時間)にVLSIシンポジウム(2023 Symposium on VLSI Technology and Circuits)において発表されます。

下線部は【用語解説】参照

※本プレスリリースでは、化学式や単位記号の上付き・下付き文字を、通常の文字と同じ大きさで表記しております。

PR TIMESのシステムでは特殊文字は使用できないため、正式な表記とは異なることご留意ください。

正式な表記でご覧になりたい方は、産総研WEBページ(https://www.aist.go.jp/aist_j/press_release/pr2023/pr20230612/pr20230612.html)をご覧ください。

開発の社会的背景

近年、材料化学計算や組合せ最適化問題など社会的に重要ないくつかの問題について、古典コンピューターを上回る高速かつ高精度な計算を実現できる量子コンピューターが注目されています。誤り訂正型量子コンピューターと呼ばれる高性能な量子コンピューターの実現に向けては、①集積されている量子ビット数の増加(目標は100万量子ビット)、②誤り発生率の低下、③1回の処理で実施できる演算回数の増加の三つを同時に実現することが求められます。今回の研究成果は、①の集積されている量子ビット数の増加と、③の演算回数の増加に関わるものです。

①の集積されている量子ビット数の増加、すなわち集積度の向上のためには、多数の量子ビットを制御するために、現在冷凍機外部に設置されている制御機能を集積回路化して冷凍機内部に設置する必要があります。超伝導型量子ビットや半導体型量子ビットを用いる場合、制御用集積回路は絶対温度4ケルビン(マイナス269.15度)の極低温環境下で動作することになり、極低温下で動作する制御用集積回路用トランジスタの開発が世界的に進められています。

③の1回の処理で実施できる演算回数の増加のためには、コヒーレンス時間と呼ばれる、量子情報を保持する時間を長くすることが求められます。コヒーレンス時間が長いほど、量子コンピューターはより多数の演算を実施することができます。コヒーレンス時間は電気的なノイズによって劣化するため、量子ビットそのものに発生するノイズや、制御用集積回路に発生するノイズを低減させる技術が大規模集積量子コンピューターの実現に向けて重要となります。

集積度の向上と演算回数の増加の両立のためには、極低温下で動作させたトランジスタのノイズを低減させる技術を確立する必要がありますが、このノイズ発生の起源が解明されていないことがノイズを低減させる技術の開発を阻んでいました。

研究の経緯

産総研は、量子コンピューターの研究開発において超伝導型量子ビットやシリコン半導体型量子ビットを用いた大規模集積化の実現を目指しています。これまでに産総研は、独自のアーキテクチャを用いた超伝導量子アニーリングマシン(2021年7月6日 産総研プレス発表)や、スピン量子ビット読み出し向け電流計測回路(2022年6月14日 産総研プレス発表)など、量子ビット素子そのものから制御用集積回路まで幅広く開発してきました。その中で、デバイス技術研究部門では制御用集積回路向けの極低温動作トランジスタ技術についての研究開発を行っており、今回、極低温動作トランジスタにおけるノイズの発生の起源を特定しました。

なお、本研究開発は、国立研究開発法人新エネルギー・産業技術総合開発機構(NEDO)の委託事業「量子計算及びイジング計算システムの統合型研究開発(2020~2027年度)」(JPNP16007)および文部科学省光・量子飛躍フラッグシッププログラム(Q-LEAP)「シリコン量子ビットによる量子計算機向け大規模集積回路の実現(2018~2027年度)」(JPMXS0118069228)による助成を受けています。

研究の内容

今回の研究は、多数のトランジスタについて極低温下におけるノイズ発生現象を統計的に実験評価し、原子サイズの欠陥に付随して生じる微小な原子位置変位が極低温動作トランジスタのノイズ発生の起源であると特定したものです。統計的な実験評価には、産総研スーパークリーンルーム(SCR)で300 mmウエハー上に作製した微細トランジスタを用いました。

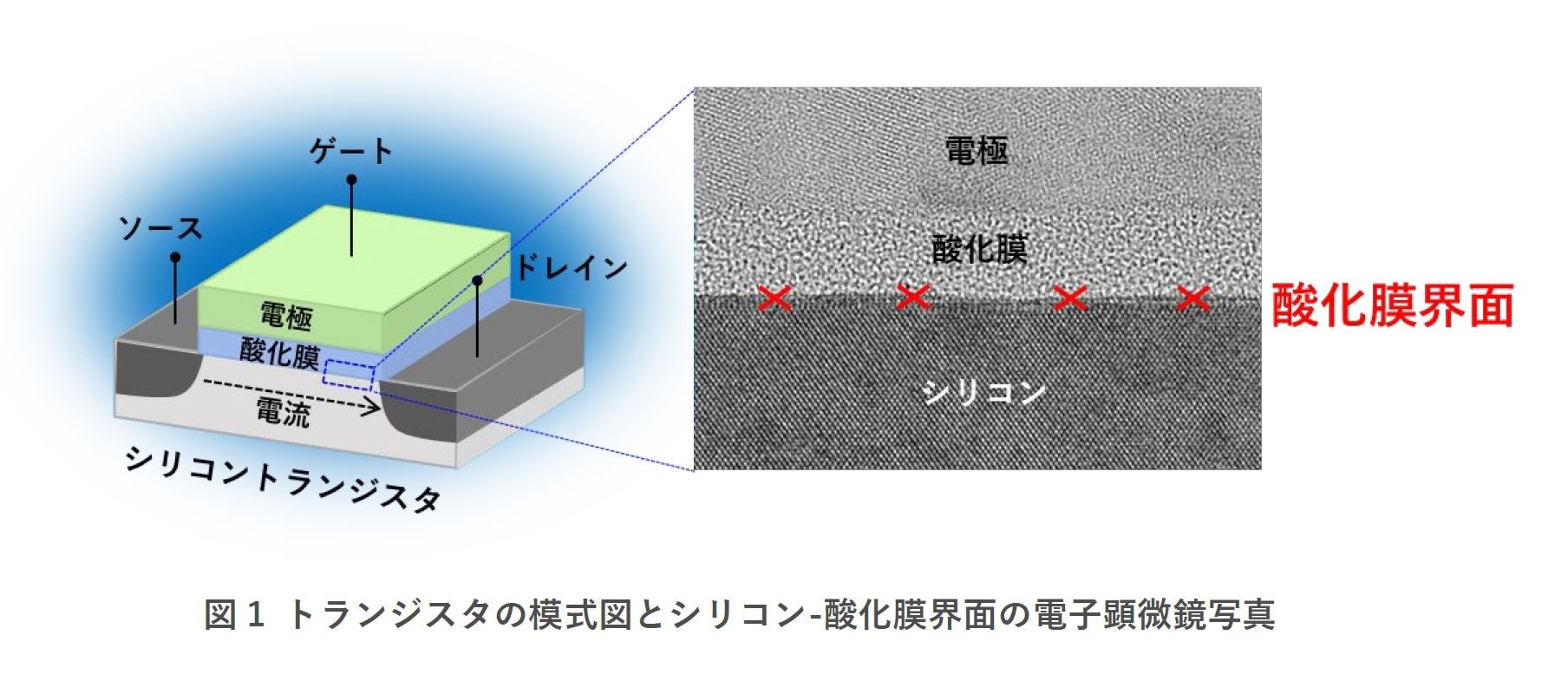

これまでの産総研の研究から、極低温動作トランジスタにおけるノイズ発生の起源が存在する場所は、トランジスタを構成するゲート電極直下のシリコン-酸化膜界面付近であることがわかっていました(図1、2020年VLSIシンポジウム発表、岡博史他)。しかし、起源の特定には至っていませんでした。

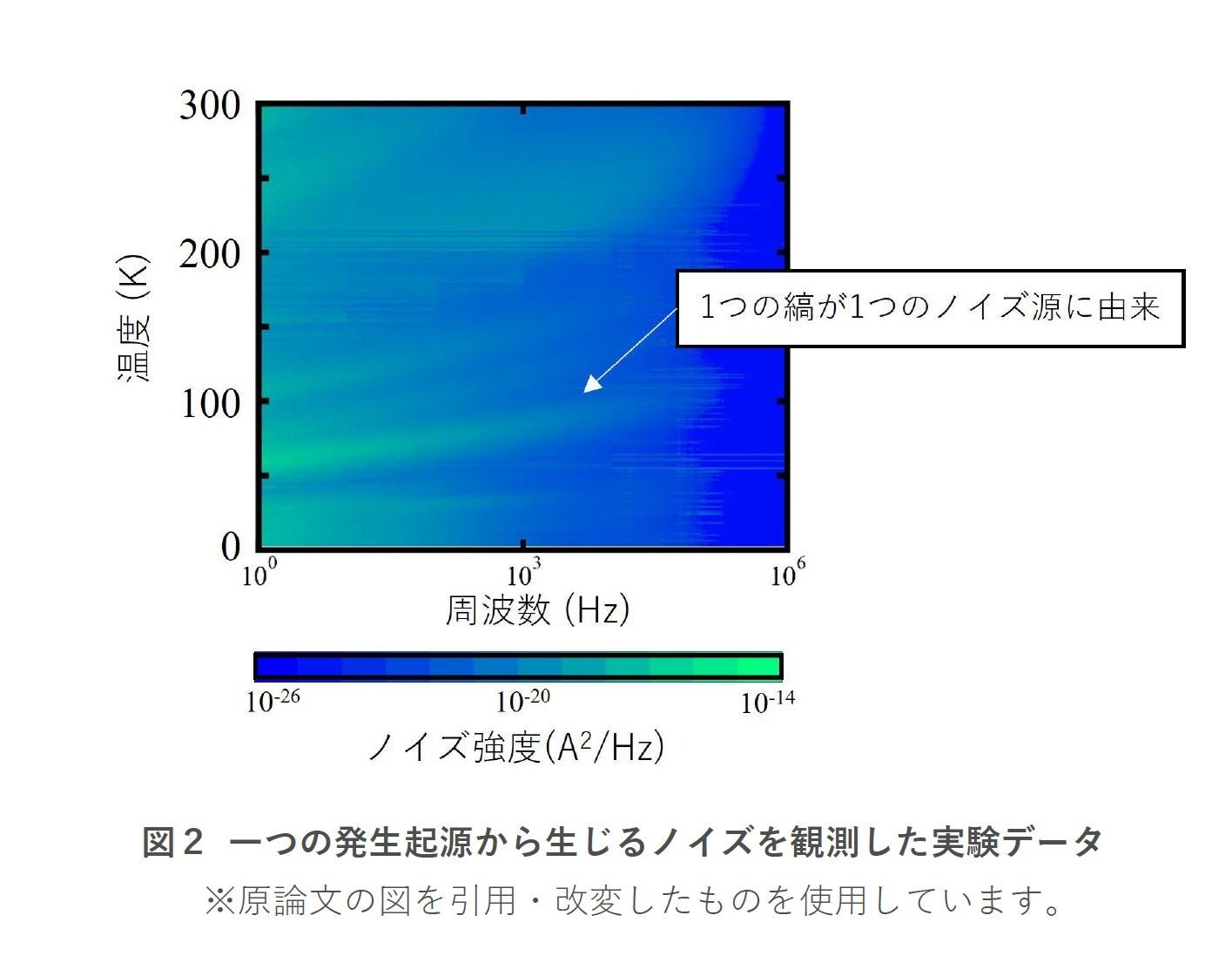

特定に至らなかった理由は、このときに用いたトランジスタが大型のものであり多数のノイズ発生の起源からの平均したノイズを観測していたことにあります。そこで今回の研究では、ノイズ発生の起源がごく少数のみ含まれるような微細なトランジスタを用いました。これにより、一つの発生の起源ごとに生じているノイズを区別して観測することに成功しました。図2は、ある一つの微細トランジスタで発生したノイズの1~106ヘルツの範囲の周波数成分の強度を、絶対温度300ケルビン(摂氏27度)から3ケルビン(摂氏マイナス270.15度)までの温度範囲で1度ずつ温度変化させながら測定したデータです。この縞(横線)一つ一つが、各温度で発生したノイズのデータです。

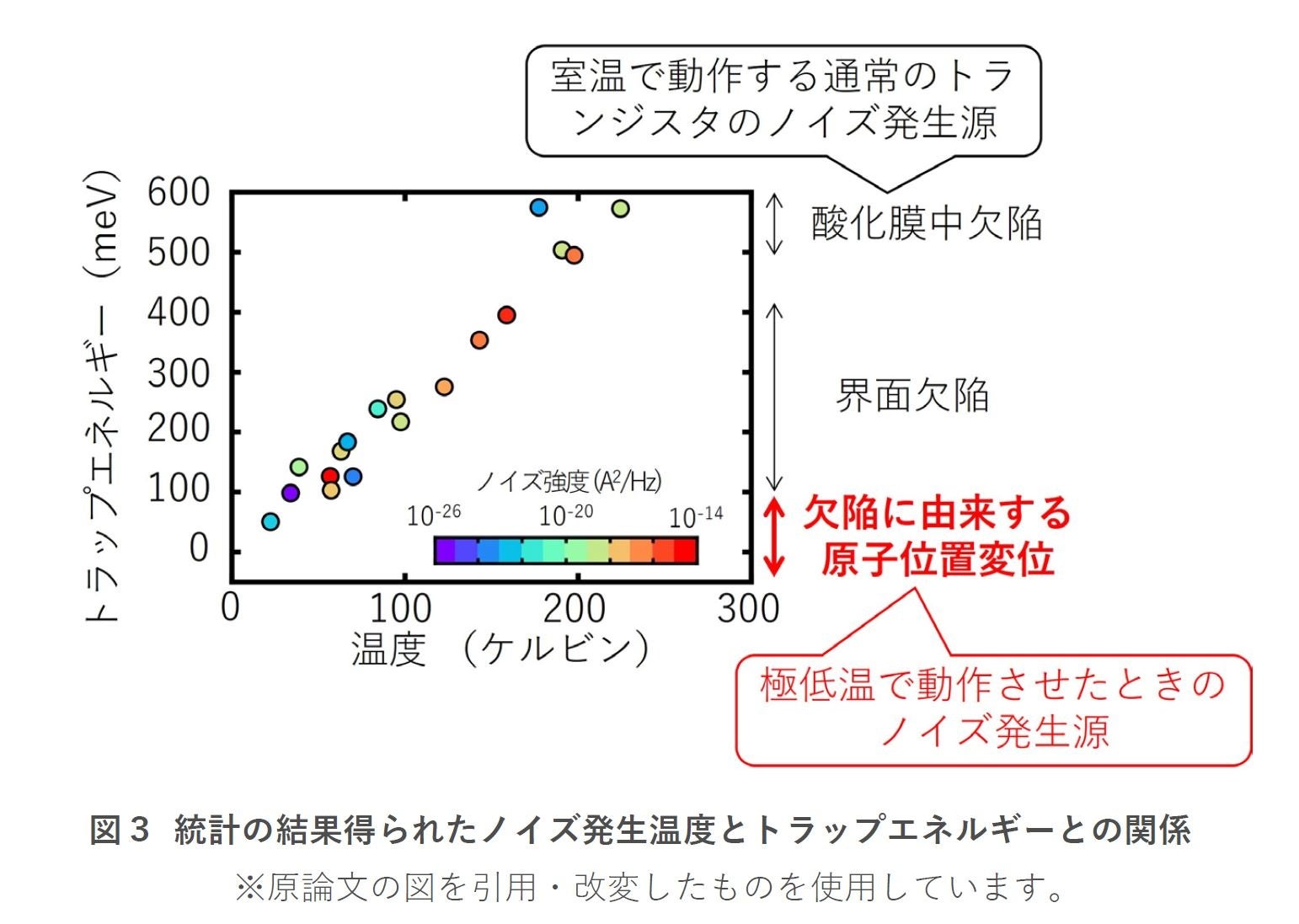

縞の様子(ノイズの各周波数成分の強度分布)を理論と比較することで、トラップエネルギーと呼ばれるノイズ発生の起源が固有に持つエネルギーを算出することができます。トラップエネルギーはノイズ発生の起源ごとに一意に決まるので、トラップエネルギーからノイズ発生の起源を特定することができます。図2で示したデータはある一つのトランジスタを測定したデータですが、別のトランジスタを測定すると縞の様子が異なるデータが得られます。そこで、多数のトランジスタを測定し、さまざまな縞のデータを取得してトラップエネルギーを算出し、統計をとります。統計をとったものが図3です。縦軸は算出して得られたトラップエネルギー、横軸はノイズが発生した温度になっています。結論として、室温に近い温度帯では酸化膜中の欠陥が主要なノイズ発生の起源であったものが、温度の低下とともに界面の欠陥が主要な発生の起源となり、極低温下ではこれらの欠陥に付随する微小な原子位置の乱れが主要なノイズ発生の起源になっていくことを明らかにしました。

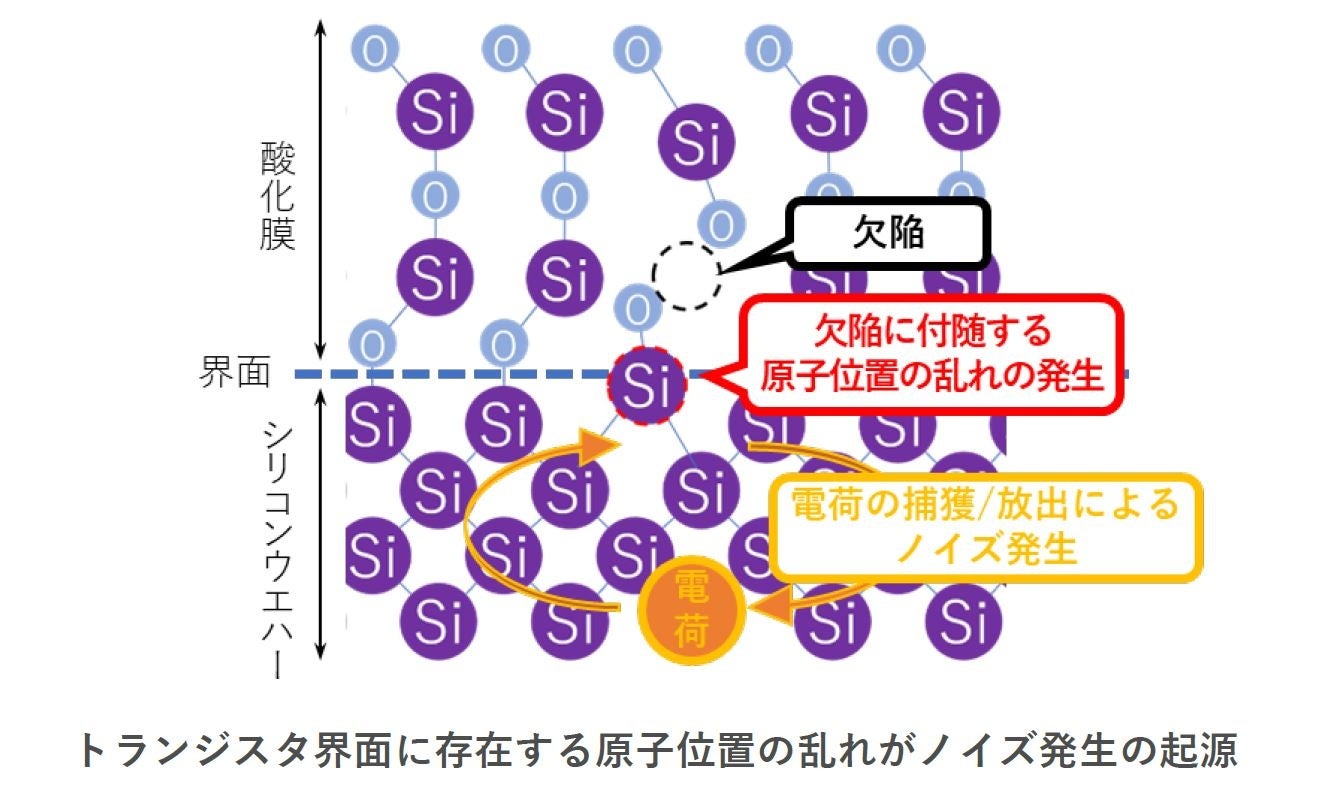

室温下でノイズ発生の起源となっている酸化膜中の欠陥は、酸化膜中の原子が一つ抜けたものです。同様に、界面欠陥も界面にあるべき原子が一つ抜けたものです。このように原子一つが抜けて欠陥ができると、それに付随して周りの原子がわずかに動き、原子位置が乱れます。これは両手をそれぞれつないでバランスをとっているときに、片方の手を離すとバランスが崩れて動いてしまうようなものです。酸化膜中の欠陥、界面の欠陥および原子位置の乱れは、電流を流している電荷を捕獲したり放出したりします。これによって電流が変動、ノイズが発生することになります。原子位置の乱れは、トランジスタを室温で動作させる場合にはノイズへの影響はほとんどありませんでした。しかし、今回の研究成果によって、極低温で動作させる場合にはこのような微小な原子位置の乱れまで考慮する必要があることがわかりました。

よって、極低温環境では微小な原子位置の乱れが生じるような欠陥を削減することでノイズを低減できます。ノイズの低減は、量子ビットのコヒーレンス時間を延ばし、量子コンピューターの1回の処理で実施できる演算回数を増加させます。このような高性能化が実現されることで、量子コンピューターの実用化に必要な性能の実現につながります。

今回得られた成果は、シリコン量子ビット素子の性能向上にも役立ちます。シリコン量子ビット素子はトランジスタと類似の素子であるため、同じノイズ発生の起源を持ちます。同じようにノイズ発生の起源を削減していくことで、シリコン量子ビット素子そのものから発生するノイズも低減化することができ、シリコン半導体型量子コンピューターの高性能化にもつながっていくと考えられます。

今後の予定

今後は今回得られた成果から、ノイズ発生起源削減技術を用いた制御用集積回路やシリコン量子ビット素子を用いた大規模集積量子コンピューターの実現を目指します。

論文情報

掲載誌:2023 IEEE VLSI Symposium on Technology and Circuits, Digest of Technical Papers

論文タイトル:Determining the low-frequency noise source in cryogenic operation of short-channel bulk MOSFETs

著者:Takumi Inaba, Hiroshi Oka, Hidehiro Asai, Hiroshi Fuketa, Shota Iizuka, Kimihiko Kato, Shunsuke Shitakata, Koichi Fukuda, and Takahiro Mori

用語解説

量子ビット素子

量子コンピューターにおいて量子情報を格納し、量子計算を実現するための素子。

トランジスタ

現代電子回路において、信号を増幅したりスイッチングしたりするための素子。

ノイズ

電気信号の小さい変動であり、誤動作の原因となるもの。素子が理想的に完全なものであれば変動は生じないが、製造品質や欠陥をゼロにはできないため、どのような素子にも少なからず発生する。

集積回路

多数のトランジスタを用いた電子回路を1枚の半導体チップの上に形成したもの。

アナログ回路

集積回路の中でも、連続的に変化するアナログ信号を取り扱うもの。電気信号はデジタル信号とアナログ信号とに大別されるが、デジタル信号は信号レベルが2個程度であるのに対し、アナログ信号は連続的な信号レベルとなる。

欠陥

半導体などの材料を構成している原子は規則的に並んでいる。その規則から外れたものを欠陥と呼ぶ。ここでは本来あるべき原子が1個無くなった点状の欠陥を指している。他にも、線状や面状の欠陥もある。

材料化学計算

薬や化粧品などに使われる化学物質の性能を予想するための計算のこと。コンピューターの性能が高く、より正しい予想ができるようになると、このような化学物質の開発スピードが向上する。

組合せ最適化問題

多くの選択肢の中から、最適なものを見つけ出す問題。電車の乗換検索や、カーナビゲーションに使われている。コンピューターの性能が高くなると、車の台数が多い、訪れる場所が多いというような、より複雑な問題を解くことができるようになる。配送便ルートの最適化が一つの例。

誤り訂正型量子コンピューター

演算する問題に制限がない量子コンピューターのこと。その実現のために演算の誤りを訂正しながら演算を実行する誤り訂正機能が必要となるため、誤り訂正型量子コンピューターと呼ばれる。 また、汎用量子コンピューターとも呼ばれることもある。

超伝導型量子ビット

超伝導材料を用いて製造される固体の量子ビット素子。超伝導型量子ビットには磁束量子ビットやトランズモン量子ビットなどと呼ばれる複数の方式がある。

半導体型量子ビット

半導体材料を用いて製造される固体の量子ビット素子。多くの場合はシリコンが用いられる。

コヒーレンス時間

量子ビット素子に格納される量子情報が保持される時間。素子によって異なる。数十ナノ秒からミリ秒まで、幅は広い。

このプレスリリースには、メディア関係者向けの情報があります

メディアユーザー登録を行うと、企業担当者の連絡先や、イベント・記者会見の情報など様々な特記情報を閲覧できます。※内容はプレスリリースにより異なります。

すべての画像