「先端半導体研究センター」を新たに設立

-研究開発から社会実装、人材育成までを担い、国内に先端半導体技術を確保-

・ ゲートオールアラウンド(GAA)構造を含む3次元デバイスを作製できる共用パイロットラインを運営

・ 研究開発と試作サービスを一体として実施するオープンイノベーション拠点として10月1日に設立

国立研究開発法人 産業技術総合研究所(以下「産総研」という)は、2023年10月1日に新たに先端半導体研究センター(略称:SFRC)を設立しました。

半導体は、私たちの生活のさまざまな場面で活用され、社会課題の解決や産業競争力強化になくてはならない存在になっています。昨今の、データ活用を推進するデジタルトランスフォーメーション(DX)や脱炭素を目指すグリーントランスフォーメーション(GX)はさらにこの流れを加速させています。そのため、経済安全保障の観点からも、半導体の重要性が増しています。経済産業省の「半導体・デジタル産業戦略」(2021年6月公開、2023年6月改訂)において、半導体製造基盤をわが国に確保するとともに、次世代技術の確立や将来技術の研究開発を推進する方針が明記されています。産総研は、これまでも、「次世代コンピューティング基盤戦略」(2022年6月)を策定するとともに、戦略の目標実現に向けた研究開発を行ってきましたが、今回、これらの活動を加速し、わが国に先端半導体技術を確保することを目標に、当研究センターを設置します。

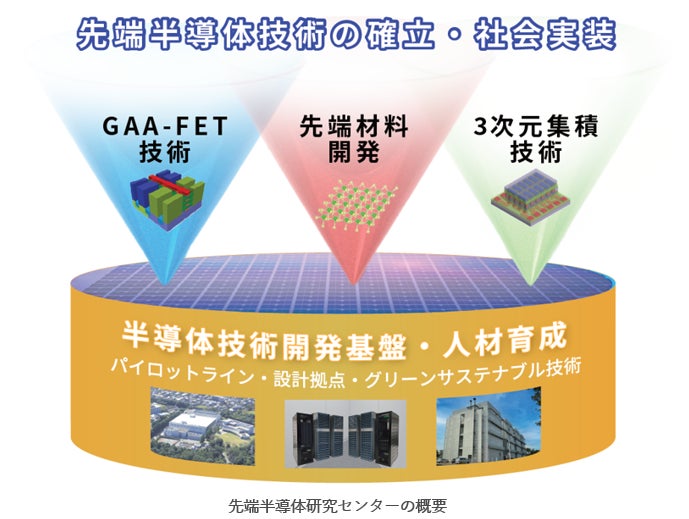

当研究センターの特徴は、研究開発、共用パイロットラインの構築、社会実装、人材育成を一貫して推進することにあります。特に研究開発においては、以下の五つの課題に重点的に取り組む予定です。

(1)2 nm世代で実用化されるゲートオ-ルアラウンド(GAA)構造の電界効果トランジスタ(FET)の基盤技術と先端構造技術の確立

(2)2 nm世代以降に向けた極限デバイス・材料開発

(3)微細化によらずに性能を向上する3次元集積技術

(4)最先端システムオンチップ(SoC)設計

(5)半導体製造の環境負荷評価およびグリーン化

これらの開発には、共用設備であるスーパークリーンルーム(SCR)や未踏デバイス試作共用拠点(COLOMODE)、AIチップ設計拠点を主に活用します。これらの設備において、研究開発と試作サービス提供、人材育成を一体として実施することにより、先端半導体のオープンイノベーションを推進する中核拠点となることを目指します。

下線部は【用語解説】参照

用語解説

デジタルトランスフォーメーション(DX)

デジタル技術を活用してまったく新しいビジネスやサービスを創出し、新たな価値を提供すること。

グリーントランスフォーメーション(GX)

脱炭素社会を目指す取り組みを通じて経済社会システムを変革させ、持続可能な成長を目指すこと。

半導体・デジタル産業戦略

経済産業省がまとめた半導体やデータセンターなどのデジタル産業支援についての政策指針。

出典:https://www.meti.go.jp/press/2023/06/20230606003/20230606003-1.pdf

次世代コンピューティング基盤戦略

日本が次世代コンピューティングハードウエア開発で取り組むべき戦略を策定・公開したもの。産総研が2022年6月に策定。

出典:https://www.aist.go.jp/aist_j/news/pr20220617.html

パイロットライン

量産の前段階で、新しい材料や工法の生産を試験的に行うための小規模の生産ライン。

ゲートオールアラウンド(GAA)構造

次世代のトランジスタ構造のひとつ。チャネル(電流の通り道)の上下左右の4面すべてをゲートで覆うことで、トランジスタを微細化した際に漏れ電流を抑えつつ高速で動作できるようにした構造。トランジスタの微細化に伴う高性能化と低消費電力化の両立のため、2~3 nm以下の世代の超微細トランジスタに導入される予定。

システムオンチップ(SoC)

演算、記憶、制御、通信などの複数の機能を統合したシステムをひとつの半導体チップ上で実現したもの。ひとつのシステムを複数のチップで実現する場合と比べて、より小型、高速、低消費電力なシステムを実現できる。

スーパークリーンルーム(SCR)

300 mmウエハーに対応した半導体プロセス装置をそろえた産総研の共用クリーンルーム施設。

未踏デバイス試作共用拠点(COLOMODE)

4インチウエハーでの多様な半導体電子デバイスの試作が可能な産総研の共用クリーンルーム施設。

出典:https://unit.aist.go.jp/d-tech/colomode/#page-top

AIチップ設計拠点

革新的なAIチップ開発を加速するために東京大学と産総研が連携して構築した半導体チップ設計拠点。

出典:AIDC for public - AIDC for public (ai-chip-design-center.org)

このプレスリリースには、メディア関係者向けの情報があります

メディアユーザー登録を行うと、企業担当者の連絡先や、イベント・記者会見の情報など様々な特記情報を閲覧できます。※内容はプレスリリースにより異なります。

すべての画像