アプライド マテリアルズ 新装置Ioniq™ PVDを投入、2Dスケーリングに伴う配線抵抗の課題を解決

アプライド マテリアルズ(Applied Materials, Inc., Nasdaq:AMAT、本社:米国カリフォルニア州サンタクララ、社長兼CEOゲイリー・E・ディッカーソン)は5月26日(現地時間)、トランジスタ配線を形成する技術を刷新して電気抵抗を大幅に低減させる新装置を投入しました。電気抵抗は、チップの性能と消費電力を改善する上で大きなボトルネックとなっていました。

半導体メーカーは、リソグラフィ技術の進歩を活用して最小線幅3nmノード以降への微細化を進めています。しかし、配線が細くなるにつれて電気抵抗は指数関数的に高まるため、チップ性能の低下と消費電力の増加をもたらします。そのため、電気抵抗のさらなる低減がなければ最先端高性能トランジスタの利点を完全に失ってしまうことになります。

チップの配線は、絶縁材料をエッチングしたトレンチとビア内に形成されます。従来の手法では配線形成にメタルスタックが用いられ、通常のスタック構成は、メタルと絶縁材料が混じることを防ぐバリア層、接着性を高めるライナー層、メタルフィルを助けるシード層、そして導電性を持つメタル(トランジスタコンタクトではタングステンやコバルト、配線には銅など)となっています。バリアとライナーはスケーリングが難しく、トレンチとビアが縮小するにつれて導電性メタルの占有スペースが相対的に減ってしまうため、線が細くなるほど電気抵抗は高くなります。

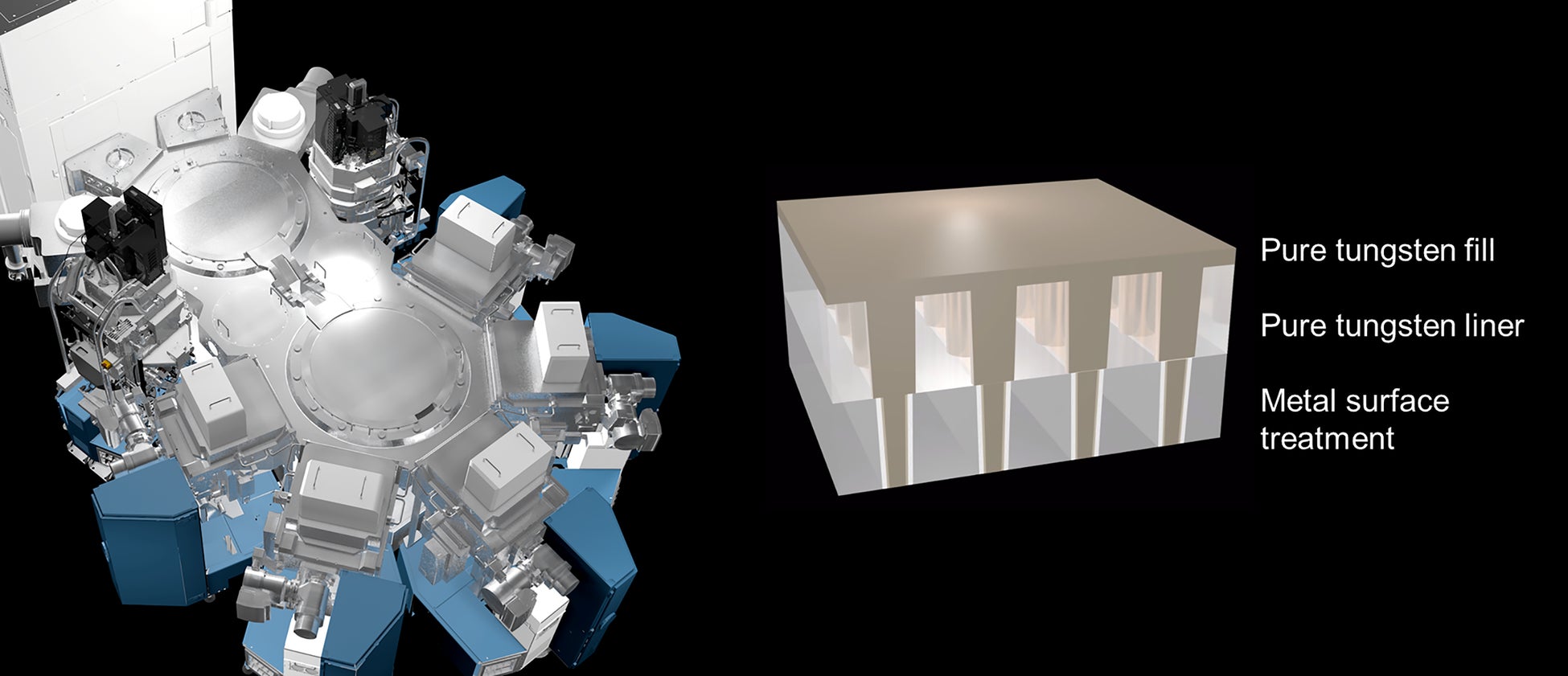

Applied Endura® Ioniq™ PVD

Ioniq PVDはインテグレーテッド マテリアルズ ソリューション(Integrated Materials Solution™:IMS™)の1つで、1台の高真空装置内にサーフェスプレパレーション、PVD、CVDの各プロセスが組み込まれています。半導体メーカーはIoniq PVDを採用することで、抵抗値の高い窒化チタン(TiN)等のライナー層とバリア層の代わりに高純度・低抵抗のPVDタングステン膜を導入することができ、これをCVDタングステンと組み合わせることでタングステンのみのメタルコンタクトが形成されます。抵抗の課題を解決するこのソリューションによって、3nmノード以降も2Dスケーリングの継続が可能となります。

アプライド マテリアルズのシニアバイスプレジデント 兼 セミコンダクタ プロダクト グループ ジェネラルマネージャー、プラブー・ラジャ(Prabu Raja)は次のように述べています。「電気抵抗増大の問題を解決するアプライド マテリアルズの最新のブレークスルーは、マテリアルズ エンジニアリングのイノベーションが2Dスケーリングの継続をもたらすことを示す顕著な例です。この革新的なIoniq PVDは、トランジスタから性能を引き出す際の大きなボトルネックを取り除き、処理の高速化と電力ロスの低減を可能にします。チップの複雑化が進むにつれ、複数のプロセスを高真空下でインテグレートする技術は重要性を増し、配線を進化させて性能と消費電力に関するお客様の目標を達成する上で不可欠となっています」

Endura Ioniq PVDは、世界各地の主要なお客さま数社に採用されています。この装置に関する詳細、および重要な配線課題の解決に向けたアプライド マテリアルズのソリューションについては、5月26日(米国時間)に当社が開催する “New Ways to Wire and Integrate Chips”と題したMaster Classで取り上げます。

アプライド マテリアルズ(Nasdaq: AMAT)は、マテリアルズ エンジニアリングのソリューションを提供するリーダーとして、世界中のほぼ全ての半導体チップや先進ディスプレイの製造に寄与します。原子レベルのマテリアル制御を産業規模で実現する専門知識により、お客様が可能性を現実に変えるのを支援します。アプライド マテリアルズはイノベーションを通じてよりよい未来を可能にします。

詳しい情報はホームページwww.appliedmaterials.com でもご覧いただけます。

********************************************************************************

このリリースは5月26日、米国においてアプライド マテリアルズが行った英文プレスリリースをアプライド マテリアルズ ジャパン株式会社が翻訳の上、発表するものです。

アプライド マテリアルズ ジャパン株式会社(本社:東京都、代表取締役社長:中尾 均)は1979年10月に設立。大阪支店、川崎オフィスのほか15のサービスセンターを置き、日本の顧客へのサポート体制を整えています。

半導体メーカーは、リソグラフィ技術の進歩を活用して最小線幅3nmノード以降への微細化を進めています。しかし、配線が細くなるにつれて電気抵抗は指数関数的に高まるため、チップ性能の低下と消費電力の増加をもたらします。そのため、電気抵抗のさらなる低減がなければ最先端高性能トランジスタの利点を完全に失ってしまうことになります。

チップの配線は、絶縁材料をエッチングしたトレンチとビア内に形成されます。従来の手法では配線形成にメタルスタックが用いられ、通常のスタック構成は、メタルと絶縁材料が混じることを防ぐバリア層、接着性を高めるライナー層、メタルフィルを助けるシード層、そして導電性を持つメタル(トランジスタコンタクトではタングステンやコバルト、配線には銅など)となっています。バリアとライナーはスケーリングが難しく、トレンチとビアが縮小するにつれて導電性メタルの占有スペースが相対的に減ってしまうため、線が細くなるほど電気抵抗は高くなります。

Applied Endura® Ioniq™ PVD

Ioniq PVDはインテグレーテッド マテリアルズ ソリューション(Integrated Materials Solution™:IMS™)の1つで、1台の高真空装置内にサーフェスプレパレーション、PVD、CVDの各プロセスが組み込まれています。半導体メーカーはIoniq PVDを採用することで、抵抗値の高い窒化チタン(TiN)等のライナー層とバリア層の代わりに高純度・低抵抗のPVDタングステン膜を導入することができ、これをCVDタングステンと組み合わせることでタングステンのみのメタルコンタクトが形成されます。抵抗の課題を解決するこのソリューションによって、3nmノード以降も2Dスケーリングの継続が可能となります。

アプライド マテリアルズのシニアバイスプレジデント 兼 セミコンダクタ プロダクト グループ ジェネラルマネージャー、プラブー・ラジャ(Prabu Raja)は次のように述べています。「電気抵抗増大の問題を解決するアプライド マテリアルズの最新のブレークスルーは、マテリアルズ エンジニアリングのイノベーションが2Dスケーリングの継続をもたらすことを示す顕著な例です。この革新的なIoniq PVDは、トランジスタから性能を引き出す際の大きなボトルネックを取り除き、処理の高速化と電力ロスの低減を可能にします。チップの複雑化が進むにつれ、複数のプロセスを高真空下でインテグレートする技術は重要性を増し、配線を進化させて性能と消費電力に関するお客様の目標を達成する上で不可欠となっています」

Endura Ioniq PVDは、世界各地の主要なお客さま数社に採用されています。この装置に関する詳細、および重要な配線課題の解決に向けたアプライド マテリアルズのソリューションについては、5月26日(米国時間)に当社が開催する “New Ways to Wire and Integrate Chips”と題したMaster Classで取り上げます。

アプライド マテリアルズ(Nasdaq: AMAT)は、マテリアルズ エンジニアリングのソリューションを提供するリーダーとして、世界中のほぼ全ての半導体チップや先進ディスプレイの製造に寄与します。原子レベルのマテリアル制御を産業規模で実現する専門知識により、お客様が可能性を現実に変えるのを支援します。アプライド マテリアルズはイノベーションを通じてよりよい未来を可能にします。

詳しい情報はホームページwww.appliedmaterials.com でもご覧いただけます。

********************************************************************************

このリリースは5月26日、米国においてアプライド マテリアルズが行った英文プレスリリースをアプライド マテリアルズ ジャパン株式会社が翻訳の上、発表するものです。

アプライド マテリアルズ ジャパン株式会社(本社:東京都、代表取締役社長:中尾 均)は1979年10月に設立。大阪支店、川崎オフィスのほか15のサービスセンターを置き、日本の顧客へのサポート体制を整えています。

このプレスリリースには、メディア関係者向けの情報があります

メディアユーザーログイン既に登録済みの方はこちら

メディアユーザー登録を行うと、企業担当者の連絡先や、イベント・記者会見の情報など様々な特記情報を閲覧できます。※内容はプレスリリースにより異なります。

すべての画像

- 種類

- 商品サービス

- ビジネスカテゴリ

- 電子部品・半導体・電気機器

- ダウンロード