パワー半導体のスイッチング損失を自動低減するゲート駆動ICチップの適用範囲を約5倍に拡大します

一般的な3端子パッケージのパワー半導体にも適用可能に

NEDOで実施している「省エネエレクトロニクスの製造基盤強化に向けた技術開発事業」(以下、本事業)において、東京大学生産技術研究所を中心とする研究グループ(以下、本研究グループ)はパワー半導体を制御してスイッチング損失を自動低減する技術(以下、本技術)を、パワー半導体の品種数の8割を占める3端子パッケージのパワー半導体にも適用可能にすることで、本技術の適用範囲を大幅に拡大することに成功しました。

本研究グループでは2023年に4端子パッケージのパワー半導体に適用してスイッチング損失を自動低減する「ゲート駆動ICチップ」を開発しましたが、4端子パッケージのパワー半導体の品種数は全体の2割程度のため、本技術の適用範囲は限られていました。今回、ゲート駆動ICチップに内蔵するセンサ回路を改良し、より汎用(はんよう)的な3端子パッケージのパワー半導体に本技術を適用できる「ゲート駆動ICチップ」を開発しました。

今回の技術改良により、「パワー半導体のスイッチング損失を自動低減するゲート駆動ICチップ」の適用対象パワー半導体は2390品種から1万1124品種へと約5倍に拡大します。本技術はシリコン(Si)のみならず、炭化ケイ素(SiC)などさまざまなパワー半導体にも適用可能です。

これにより、省エネルギー技術の普及が加速し、パワーエレクトロニクス機器の省エネ化による温室効果ガスのさらなる排出量削減に貢献します。

1.背景

パワーエレクトロニクス機器の分野では、さらなる省エネ化の要求に応えるため、さまざまなパワー半導体の低スイッチング損失化に関する研究開発が行われてきました。本研究グループでは、パワー半導体の「ゲート端子を最適に駆動する」という、「使いこなし」の視点から、パワー半導体のスイッチング損失※1を低減する研究開発を進め、2023年に4端子パッケージのパワー半導体に適用できる「スイッチング損失を自動低減するゲート駆動ICチップ」※2を開発しました。

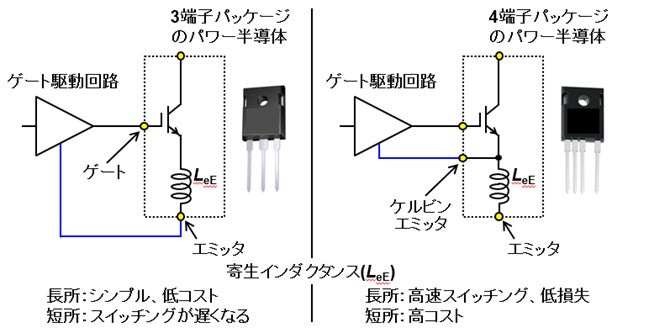

一般にパワー半導体は、3端子と4端子の2種類のパッケージ品があります(図2)。4端子パッケージのパワー半導体では、ソース側の配線の抵抗成分やインダクタンス成分の影響を受けないケルビンエミッタ端子が追加されており、この端子とゲート端子間の電圧VGSを制御することで、ターンオン・オフの高速スイッチングが可能になります。反面、4端子パッケージのパワー半導体は3端子パッケージ品に対して高コストであるために適用アプリケーションが限定される課題があります。主要パワー半導体メーカー10社の製品調査によると、4端子パッケージ品が2390品種に対して、3端子パッケージ品は8734品種あります。そのため、以前開発した「スイッチング損失を自動低減するゲート駆動ICチップ」が適用できる4端子パッケージのパワー半導体の品種数は全体の2割程度にすぎない課題がありました。

このような背景を踏まえ、NEDOが2021年度から進める本事業※3の中で大口径インテリジェント・シリコンパワー半導体の開発に取り組む研究開発の一環として、本研究グループでは、3端子パッケージのパワー半導体にも適用可能な「スイッチング損失を自動低減するゲート駆動ICチップ」の開発に取り組んできました。

2.今回の成果

(1)3端子パッケージのパワー半導体にも適用できる「スイッチング損失を自動低減するゲート駆動ICチップ」の開発

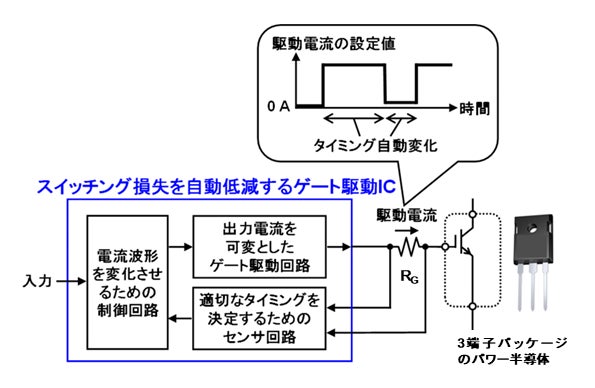

開発したゲート駆動ICチップは図3に示すようにパワー半導体のゲート駆動電流(ゲート端子に挿入されたセンス抵抗RGの両端電圧から検出)をセンシングする方式を採用することで、パワー半導体の品種数の約8割を占める3端子パッケージのパワー半導体にも適用可能となりました。

また、本「スイッチング損失を自動低減するゲート駆動ICチップ」は実証に使用したシリコンパワー半導体のみならず炭化ケイ素(SiC)などさまざまなパワー半導体のゲート駆動用に適用可能です。

また、本ICチップは以下の特長を備えています。

●動作条件の変動に適応

パワー半導体の負荷電流や温度などの動作条件が変化しても、ゲート駆動電流のタイミングを自動調整し、スイッチング損失を常に低減。

●省スペース・低コスト

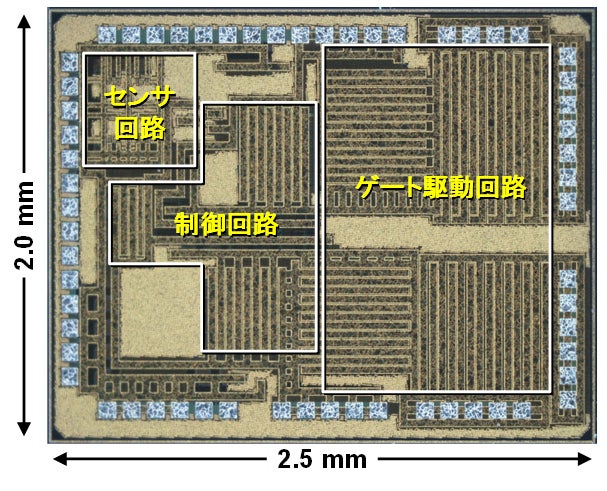

センサ回路、制御回路、ゲート駆動回路の三つの機能を1チップ化することで、従来のゲート駆動ICチップとそのまま置き換え可能。追加の回路設計や外付け部品を必要とせず、コンパクトかつ低コストで導入可能。

(2)本ICチップと3端子パッケージのパワー半導体とを組み合わせた測定系にてスイッチング損失の自動低減を実証

今回開発したICチップでゲート制御した3端子パッケージのパワー半導体のスイッチング損失の低減効果を検証するため、ゲート駆動ICチップとシリコンの3端子パッケージのパワー半導体(定格電圧1200V、定格電流100AのIGBT)を組み合わせた測定系を開発し、パワー半導体をスイッチング動作させる実証試験を行いました。出力600V、負荷電流20A、50A、80Aの3条件および温度25℃、75℃、125℃の3条件を組み合わせた9条件にて、汎用のゲート駆動ICでの制御に比べて、ゲート駆動ICチップで制御した3端子パッケージのパワー半導体のスイッチング損失は16%から30%低減することが実証できました※4。

3.今後の予定

NEDOと東京大学生産技術研究所を中心とする研究グループは本事業において、さらなる高耐圧パワー半導体のスイッチング損失を低減する自動最適化手法※5やセンシング誤差※6を改善したセンサ回路の開発、それらを搭載したゲート駆動チップICの開発と実証を進めます。

【注釈】

※1 スイッチング損失

パワー半導体の出力電流のオンオフ切り替えの際に発生する電力損失のことです。

※2 「スイッチング損失を自動低減するゲート駆動ICチップ」

「世界初、パワー半導体を自動で最適に制御し、損失を低減するICチップを開発―パワー半導体のエネルギー損失を約49%低減―」(2023/3/23) https://www.nedo.go.jp/news/press/AA5_101618.html

※3 本事業

事業名:省エネエレクトロニクスの製造基盤強化に向けた技術開発事業

事業期間:2021年度~2025年度

事業概要:省エネエレクトロニクスの製造基盤強化に向けた技術開発事業

https://www.nedo.go.jp/activities/ZZJP_100192.html

※4 スイッチング損失は16%から30%低減することが実証できました

研究成果は、2025年3月16日から20日まで米国・アトランタで開催されているIEEE Applied Power Electronics Conference and Exposition (APEC) 2025 で発表されます。(論文タイトル:”Fully Integrated Closed-Loop Active Gate Driver IC With Real-Time Control of Gate Current Change Timing by Gate Current Sensing”)

※5 自動最適化手法

パワー半導体の状態に応じてエネルギー損失とノイズのバランスを自動で最適化する手法です。

※6 センシング誤差

パワー半導体の状態を示す温度や電圧などの測定誤差を指します。

このプレスリリースには、メディア関係者向けの情報があります

メディアユーザー登録を行うと、企業担当者の連絡先や、イベント・記者会見の情報など様々な特記情報を閲覧できます。※内容はプレスリリースにより異なります。

すべての画像