TOPPAN、世界初の単体での電気検査が可能な次世代半導体向けコアレス有機インターポーザーを開発

インターポーザーの不良に起因するチップの廃棄ロスの大幅な削減に貢献

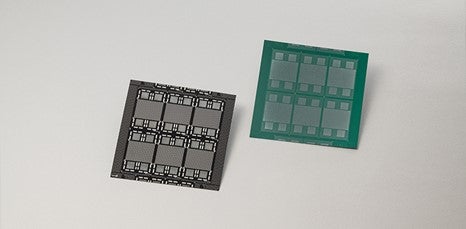

今回開発した次世代半導体向けコアレス有機インターポーザーは、再配線層(RDL)の両面を低CTE(熱膨張率)の材料で補強したものです。シンプルなコアレス構造で、微細配線接続と低CTEの両立を図りつつ、剛直性の付与を実現しています。これにより有機インターポーザー自体を支持体(キャリア)から自立させることができ、世界で初めて(TOPPAN調べ)有機インターポーザー単体での電気検査保証が可能になりました。信頼性がより高まり、インターポーザーの不良に起因するチップの廃棄ロスの大幅な削減に貢献することができます。

なお本製品は、6月12日(水)~14日(金)に東京ビッグサイトで開催される「電子機器トータルソリューション展 2024」のTOPPANブースで出展予定です。

■本製品開発の背景

半導体の高機能化において、インターポーザー上に異種複数チップを集積するヘテロジニアスインテグレーション(異種チップ集積)が主流となっています。現在は、シリコンインターポーザーが主流ですが、コストの観点から将来的には有機インターポーザーを採用した半導体パッケージの普及が見込まれています。しかし、一般的な有機インターポーザーは構造的に剛直性に乏しく、単体でのハンドリングが困難なため、電気検査時には支持体等に固定する必要があり、その状態では、表裏の導通の確認ができないことが課題でした。

TOPPANが今回開発した次世代半導体向けコアレス有機インターポーザーは、再配線層(RDL)の両面を低CTEの材料で補強したものです。シンプルなコアレス構造で、微細配線接続と低CTEの両立を図りつつ、剛直性の付与を実現します。これにより有機インターポーザー自体を支持体(キャリア)から自立させることができ、有機インターポーザー単体での電気検査保証が可能となります。

有機インターポーザーに不良があった場合は、インターポーザーに実装したLSIチップまで廃棄しなければなりませんが、あらかじめ電気検査保証された、信頼性の高い有機インターポーザーであれば、チップの廃棄ロスを大幅に削減することが可能になります。

コアレス有機インターポーザーの断面構造イメージ ©TOPPAN Inc.

コアレス有機インターポーザーの断面構造イメージ ©TOPPAN Inc.

■ 本製品の特長

1) 製造工程の途中で支持体から自立することで、単体での電気検査保証が可能で信頼性を高めること ができ、Known-good substrate(あらかじめ信頼性が確認できている基板)としての供給が可能。

2) 従来パッケージ基板よりも約45%の低熱膨張を実現。FC-BGA基板とRDLの熱膨張係数の差に起因するクラック(割れ)を抑止できます。

3) 狭ピッチモールド樹脂貫通電極(TMV)構造により、最小接続端子ピッチはチップ側で40μm(従来130μm)、基板側で130μm(従来300μm)のファインルーティング/ファインインターコネクトを実現。

4) パネルレベル製造のスケーラビリティにより、100㎜超の大型インターサイズにも対応可能。

■ 今後の展開

TOPPANは、本製品をデータセンター向けサーバーCPU、AIアクセラレーター向けなどの半導体パッケージ基板および有機インターポーザーへの採用を目指します。また、本構造を含む次世代半導体パッケージ関連製品を2027年度からサンプル提供、2028年度から量産を開始する予定です。

■「電子機器トータルソリューション展 2024」について

・会期: 2024年6月12日(水)~14日(金)10:00~17:00

・会場:東京ビッグサイト 東ホール

※TOPPANは「JPCA Show 2024」に出展(東3ホール/小間番号3A-28)

・主催:一般社団法人日本電子回路工業会、一般社団法人エレクトロニクス実装学会、一般社団法人日本ロボット工業会

・公式サイト:https://www.jpcashow.com/show2024/jp/exhibition/index.html

※1インターポーザー

貫通電極によって表裏の回路を電気的に接続するために用いられる基板

* 本ニュースリリースに記載された商品・サービス名は各社の商標または登録商標です。

* 本ニュースリリースに記載された内容は発表日現在のものです。その後予告なしに変更されることがあります。

以 上

このプレスリリースには、メディア関係者向けの情報があります

メディアユーザー登録を行うと、企業担当者の連絡先や、イベント・記者会見の情報など様々な特記情報を閲覧できます。※内容はプレスリリースにより異なります。

すべての画像