図研、SEMICON Japan 2024でチップレット集積半導体開発を見据えたソリューションを提案

Synopsys社、Ansys社と協調したトータルソリューションを展示

株式会社図研(神奈川県横浜市、代表取締役社長 勝部 迅也、以下図研)は、2024年12月11~13日に東京ビッグサイトで開催されるSEMICON Japan 2024に出展し、3D-ICやチップレット、先端半導体パッケージの設計や、半導体製造装置開発などを支援するソリューションを展示します。

同イベントにおいて今回新設された、次世代の半導体設計と検証分野にフォーカスする主要EDAベンダを集めた新たな「ADIS(Advanced Design Innovation Summit)」ゾーンに出展し、テクノロジーパートナーであるSynopsys社、Ansys社とも協調して、新たな半導体開発を総合的に支援する設計ソリューションを紹介します。

半導体開発は、配線微細化の技術的な限界や開発・製造コストの問題などから、モノリシックなSoCから、チップレットや3D-ICといったヘテロジニアスインテグレーション(異種チップ集積)へとシフトしようとしています。こうした新たなテクノロジーは、技術やコストの課題を克服するとともに、自動車業界をはじめとしたさまざまな業界でより独自性のある高性能の半導体開発を可能にすることが期待されています。しかし、このチップレットや3D-ICの開発においては、個々のチップだけでなく、チップ間やインターポーザ、パッケージまで含めたシステムとして歩留まりを向上するための最適な設計・解析環境が求められます。

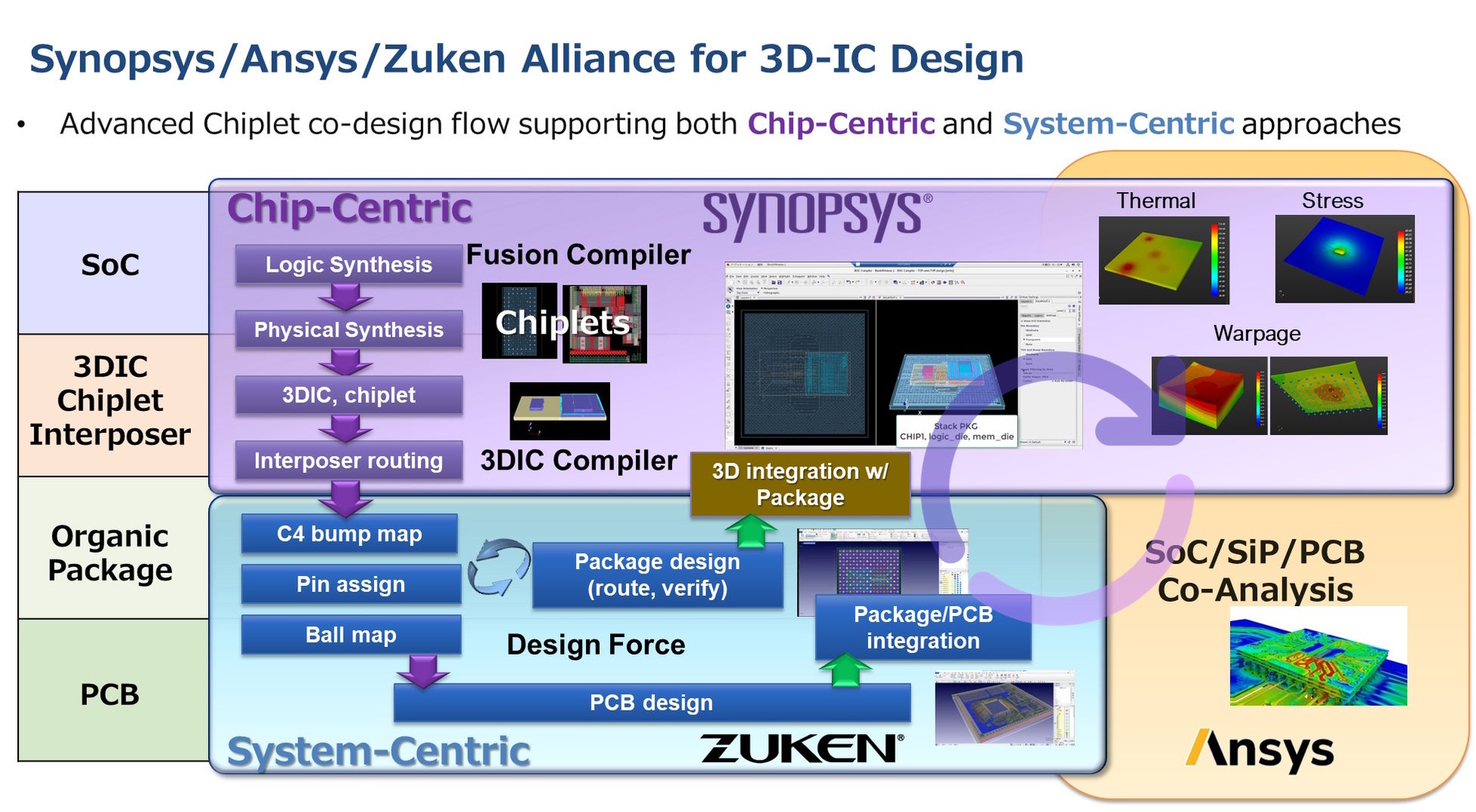

そこで、図研はこうしたニーズに応えていくために、半導体開発上流工程向けソリューションと幅広い領域に適応できる解析ソリューションにおいて業界最高レベルのツールを持つSynopsys社、Ansys社と協調し、新たな3D-IC設計・解析をターゲットにした総合的な開発環境の提供に取組んでいます。具体的には、チップレット設計で業界標準となりつつあるSynopsys社の3DIC Compilerと、図研のシステムレベルマルチボード設計・検証環境 CR-8000 Design Forceをシームレスに連携した設計フローをサポートする機能を開発しています。また、すでにCR-8000 Design Forceとタイトに連携しているAnsys社の解析ソリューションを加え、先端半導体パッケージ設計において必要とされるシステム全体を考慮した開発環境を実現していきます。(上図参照)

同イベント期間中、図研ブースではチップレットや3D-IC、先端半導体パッケージの設計支援について、各社からのプレゼンテーションもまじえて紹介するセミナーを随時開催します。

また、12月12日(木)12:30~14:10に開催される「ADIS(Advanced Design Innovation Summit)」内で開催されるパネルディスカッション“「EDAベンダが語る」設計現場の最前線”において、図研専務執行役員 CTO 技術本部長 仮屋 和浩がパネリストとして参加します。ぜひ会場にてご覧ください。

■ADIS(Advanced Design Innovation Summit)について

半導体前工程、後工程の設計・検証・解析ツールを提供する主要EDAベンダと、そのユーザを代表する団体・企業が参加し、新たな時代に相応しい設計環境について交流や情報交換を行っています。

■SEMICON Japan 2024 出展概要

-

日時:2024年12月11日(水)~13日(金) 10:00~17:00

-

会場:東京ビッグサイト 東1~8ホール

小間情報:ADIS内:東2ホール 小間番号2822・2823

未来COLLEGE内:東7ホール 小間番号7920

-

入場料:事前来場登録で無料(セミナーは一部有料)

-

主催:SEMIジャパン

■パネルディスカッション 「EDAベンダが語る」設計現場の最前線

・日時:2024/12/12(木) | 12:30 - 14:10(東7ホール TechSTAGE SAKURA)

各EDAベンダが、ベンダの垣根を越えて、今後の設計や検証について熱い議論を交わします。チップレット使用を想定した半導体回路設計、パッケージング、システムレベルの設計や検証について現状を整理し、課題を洗い出し、将来の向かうべき方向性を議論します。

・パネリスト:

仮屋 和浩 図研 専務執行役員 CTO 技術本部長

丁子 和之 シーメンスEDAジャパン 技術本部 技術本部長

古賀 一成 日本シノプシス EDAG

人見 忠明 日本ケイデンス・デザイン・システムズ AEマネージャー

大塚 慶太郎 MathWorks Japan アプリケーションエンジニアリング部 部長

Bill Baker Ansys Asia Semiconductor Sales Director

モデレーター:

川原 伸章 自動車用先端SoC技術研究組合 専務理事

石田 光也 Rapidus 3Dアセンブリ企画部 部長

「図研」および図研製品の名称は、株式会社図研の登録商標または商標です。その他、記載されている会社名、製品名などの固有名詞は、各社の商標または登録商標です。

このプレスリリースには、メディア関係者向けの情報があります

メディアユーザー登録を行うと、企業担当者の連絡先や、イベント・記者会見の情報など様々な特記情報を閲覧できます。※内容はプレスリリースにより異なります。

すべての画像