半導体デバイスの3次元技術に寄与する後工程向けi線半導体露光装置を発売 100×100mmの超広画角による大型・高密度配線パッケージの量産を実現

FPA-5520iV LF2オプション

FPA-5520iV LF2オプション

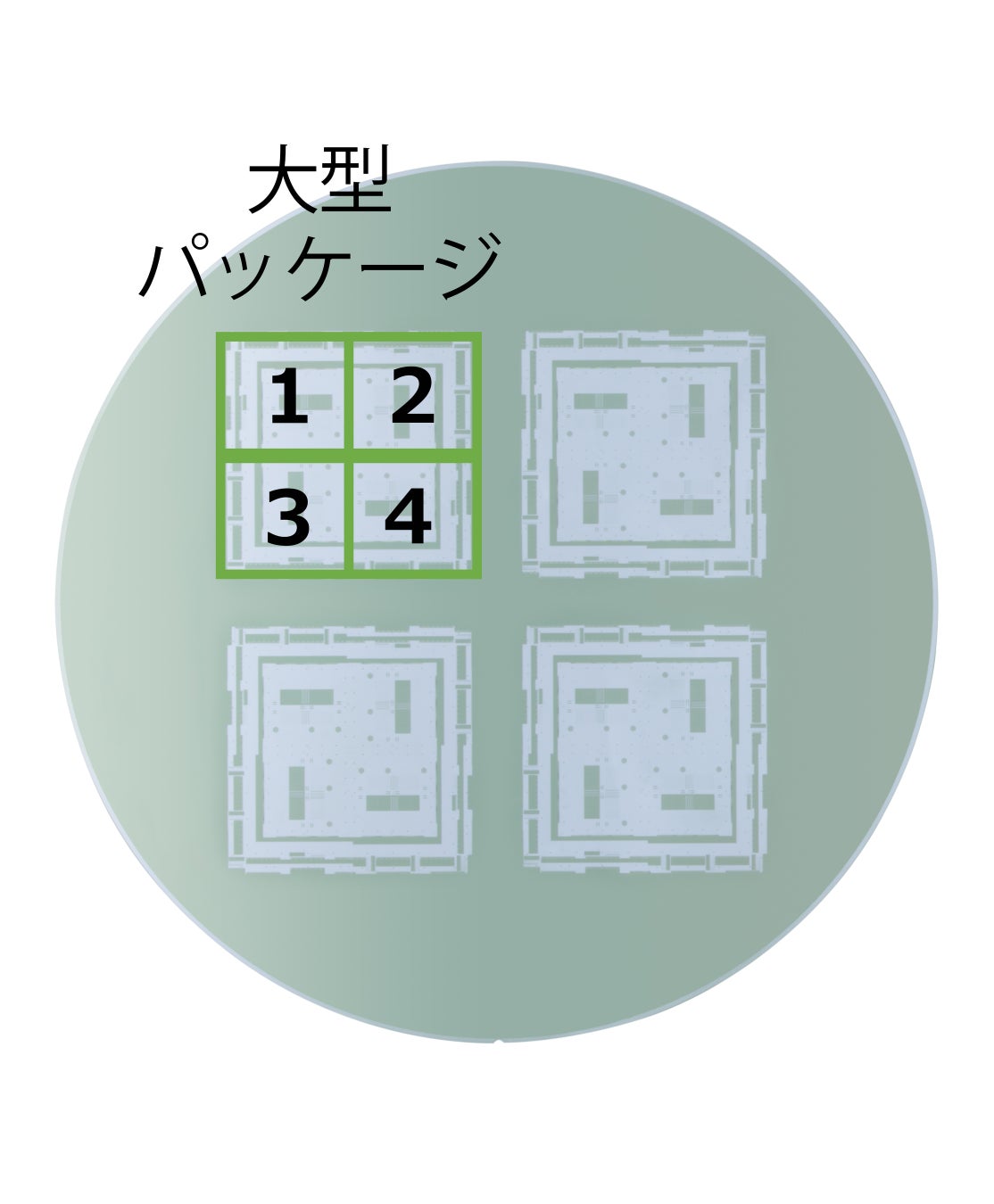

4つの露光ショットを繋ぎ合わせて1つの大型パッケージとする例(4ショット×4個)

4つの露光ショットを繋ぎ合わせて1つの大型パッケージとする例(4ショット×4個)

半導体チップの高性能化においては、半導体製造の前工程での回路の微細化だけでなく、後工程で行われるパッケージングでの高密度化が注目されています。高密度化を実現する先端パッケージングには、微細な配線が必要で、近年では半導体露光装置が使用されるようになっており、複数の半導体チップを並べて密接に接続する2.5次元技術(※3)や、半導体チップを積層する3次元技術(※4)により、半導体デバイスの性能を向上したいというニーズがあります。

新製品は、0.8μmの高解像力と露光ひずみの小さい4ショットの繋ぎ露光による100×100mmの超広画角の露光を可能とすることで、2.5次元と3次元技術を組み合わせた超大型・高密度配線パッケージの量産を実現します。

1. 新投影光学系と照明光学系の改善により0.8μmの高解像力と繋ぎ露光による超広画角を実現

従来機種「FPA-5520iV LFオプション」(2021年4月発売)と比べ、歪曲収差を4分の1以下にまで改善した新投影光学系の搭載と、照度均一性を高めた照明光学系の採用により、52×68mmの広画角でありながら0.8μmの解像力と、繋ぎ露光による100×100mmの超広画角を実現します。

2. 「FPA-5520iV」の基本性能を継承

パッケージング工程での量産課題である再構成基板(※5)の反った形状に対する柔軟な対応力とともに、チップ配列のばらつきが大きい再構成基板でもアライメントマークを検出し稼働率を向上させる高い生産性など、「FPA-5520iV」で実現した基本性能を継承しています。

キヤノンは、半導体チップを製造する前工程だけではなく、後工程での先端パッケージング技術に対応する半導体露光装置のラインアップも拡充することで、さらなる半導体デバイスの技術革新に貢献します。

※1. 1µm(マイクロメートル)は、100万分の1メートル(=1000分の1mm)。

※2. i線(水銀ランプ波長365nm)の光源を利用した半導体露光装置。1nm(ナノメートル)は10億分の1メートル。

※3. パッケージ基板上にシリコンインターポーザ(半導体チップとパッケージ基板の間を電気的に接続する中継部材)を置き、その上に複数の半導体チップを並べて密接に接続する技術。

※4. TSV技術(シリコン貫通電極技術。高集積化を実現するために、シリコンの表と裏を貫通させる技術)により積層する技術。

※5. 半導体露光装置の前工程で製造されたウエハーから個片化された複数の半導体チップを配列し、樹脂でウエハー形状に固めた基板。

このプレスリリースには、メディア関係者向けの情報があります

メディアユーザー登録を行うと、企業担当者の連絡先や、イベント・記者会見の情報など様々な特記情報を閲覧できます。※内容はプレスリリースにより異なります。

すべての画像