ケイデンス、チップレットの市場投入を加速するパートナーエコシステムを発表

Samsung Foundry、Arm社などとの戦略的協業によりCadence Physical AIチップレットプラットフォームを基盤とした事前検証済みチップレットソリューションを提供

ケイデンス(本社 米国カリフォルニア州サンノゼ市)は、1月6日(米国時間)、フィジカルAI、データセンター、高性能コンピューティング(HPC)向けチップレット開発における設計の複雑さを軽減し、市場投入までの期間を短縮することを目的とした「Chiplet Spec-to-Packaged Partsエコシステム」を発表しました。初期IP提供パートナーにはArm社、Arteris社、eMemory社、M31 Technology社、Silicon Creations社、Trilinear Technologies社が、半導体解析技術パートナーにはproteanTecs社が参加しています。リスクを低減し、チップレットの採用をスムーズにするため、

ケイデンスはSamsung Foundryと協力して、同社のSF5Aプロセス上でパートナー提供のIPを事前統合したCadence® Physical AIチップレットプラットフォームを基盤とした半導体試作品のデモを構築します。

ケイデンスとArm社は長年の緊密な協業関係をさらに拡大し、フィジカルAIおよびインフラAI分野のイノベーション加速に取り組んでいます。今後、ケイデンスではArm® Zena™ Compute Subsystem(CSS)やその他の主要IPを活用して、Physical AIチップレットプラットフォームおよび

Chiplet Frameworkを強化します。これにより、自動車、ロボティクス、ドローンの次世代エッジAI向け処理要件に加えて、データセンター、クラウド、HPCで必要とされる標準I/O・メモリチップレットのニーズに対応します。今回の協業により設計の複雑さを軽減することで、低リスクで先進的なチップレット導入への道を開き、よりスマートで安全かつ効率的なシステムの実現を後押しします。

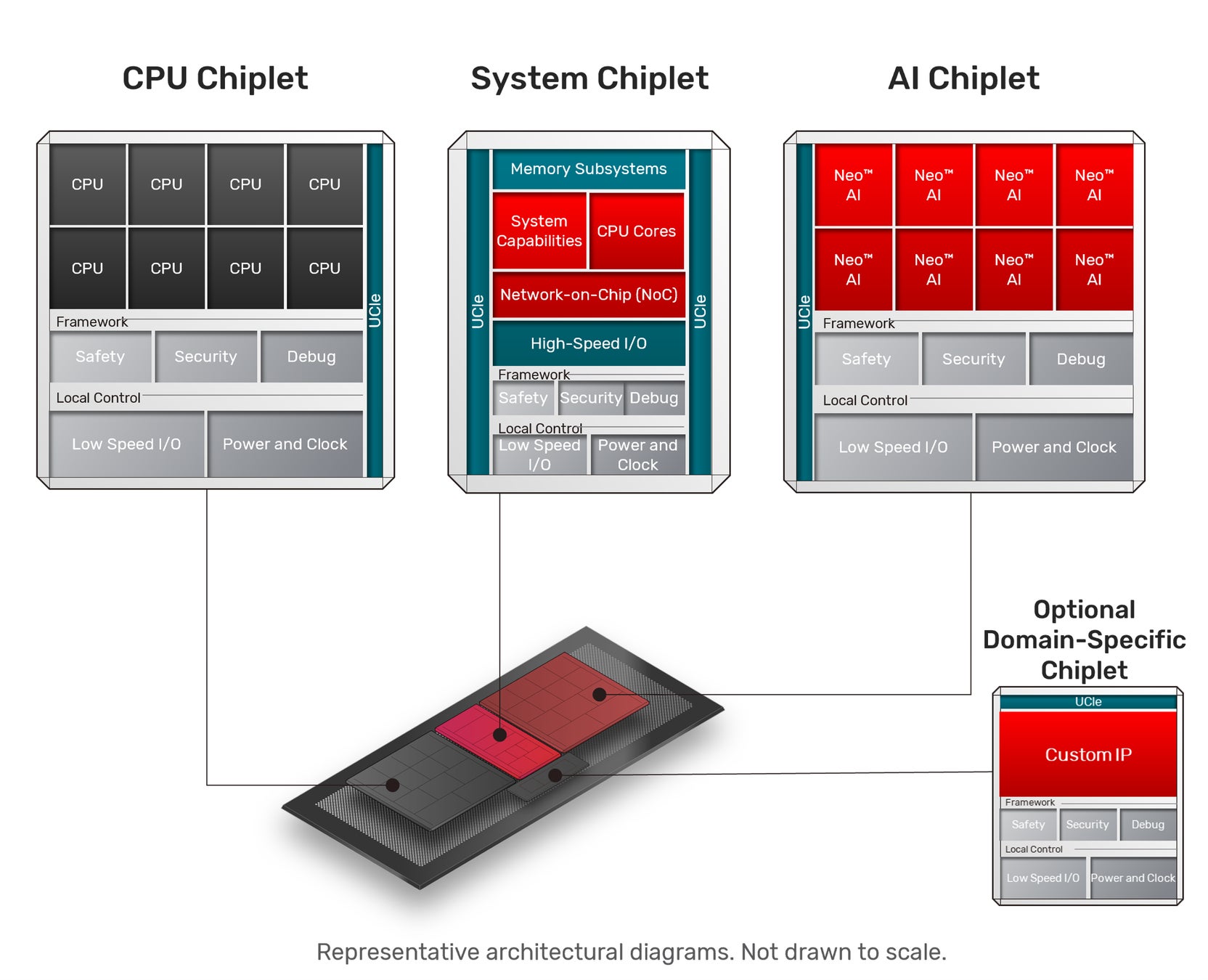

ケイデンスは、仕様に基づく自動化により、自社とサードパーティパートナーのIPにチップレット管理・セキュリティ・安全機能を組み合わせたチップレットフレームワークアーキテクチャを構築しています。生成されたEDAフローは、Cadence Xcelium™ Logic Simulatorによるシミュレーション、

Cadence Palladium® Z3 Enterprise Emulation Platformによるエミュレーションをシームレスに実現し、物理設計フローではリアルタイムフィードバックによる効率的な配置配線プロセスを可能にします。生成されたチップレットアーキテクチャは、Arm Chiplet System Architectureや将来策定されるOCP Foundational Chiplet System Architectureなどの標準に準拠し、エコシステム全体での広範な相互運用性を確保します。さらに、ケイデンスのUniversal Chiplet Interconnect Express™

(UCIe™)IPは業界標準のダイ間接続を実現し、包括的なプロトコルIPポートフォリオはLPDDR6/5X、DDR5-MRDIMM、PCI Express®(PCIe®)7.0、HBM4など最先端インターフェースの迅速な統合を可能にします。

パートナー各社コメント

Arm社

Suraj Gajendra氏(Vice President of Products and Solutions, Physical AI Business Unit)

「自動車、ロボティクスなど新興分野で計算処理の需要が急増する中、業界は高性能・高効率・機能安全を設計段階から実現できる拡張性の高いソリューションを求めています。Arm Zena CSSを活用することで、ケイデンスのチップレットプラットフォームは次世代インテリジェントシステムの要件を満たし、フィジカルAI分野の進化とチップレット導入の加速、そして設計の複雑さの軽減に貢献します。」

Arteris社

Guillaume Boillet氏(Vice President of Strategic Marketing)

「イノベーションを牽引している当社のネットワークオンチップIP製品(Ncore、FlexNoC)が、ケイデンスのPhysical AI Chiplet PlatformとChiplet Frameworkをサポートできることを大変嬉しく思います。ケイデンスと共に、高帯域幅でスケーラブル、量産実績のあるインターコネクト技術を活用し、次世代マルチダイシステムにおけるチップレットアーキテクチャの採用を促進します。」

eMemory社

Charles Hsu氏(Chairman)

「当社の高機能OTP製品は、ケイデンスのSecuryzr™ Root of Trustと組み合わせることで、Cadence Chiplet Frameworkにおけるセキュリティを強化します。また、不揮発性メモリ技術のリーディングプロバイダーである当社の技術とケイデンスのセキュリティサブシステムを統合することで、安全なストレージと長期ライフサイクルの鍵管理を実現し、先進的なチップレット設計におけるダイ間のセキュリティと安全性を確保する強固なハードウェア基盤を提供できます。」

M31 Technology社

Scott Chang氏(CEO)

「ケイデンスが拡大するチップレット・エコシステムに貢献できることを誇りに思います。本エコシステムは、最先端プロセス技術におけるインターフェースIPを継続的に進化させ、最新のMIPI規格に対応し続けています。当社は、車載グレードIPの実績と、大量生産されるコンシューマ製品を10年以上支えてきた経験を活かし、業界最高水準のMIPI PHYインターフェースIPを提供します。これにより、MIPI CSIとDSIを柔軟に統合し、先進的なチップレットソリューションを迅速に実現できます。」

proteanTecs社

Ziv Paz氏(VP of Business Development)

「ケイデンスのチップレットプラットフォームと提携し、あらゆるチップレットに当社のテレメトリを組み込めることを大変嬉しく思います。ケイデンスと共に、次世代コンピューティングの需要に応える、安全性・信頼性・電力効率に優れたフィジカルAIを実現します。この協業により、車載や自動運転向けの先進的なSoCやシステムを開発するお客様に、確かな価値をお届けします。」

Samsung Electronics社

Taejoong Song氏(Vice President of Foundry Technology Planning)

「ケイデンスとの協業により、当社のSF5A技術が持つ優位性を実証できることを嬉しく思います。この強固なパートナーシップを通じて、Chiplet Spec-to-Packaged Partsエコシステムの拡大を目指します。さらに、フィジカルAI分野、特に次世代車載システムの設計向けに、お客様が最先端の半導体ソリューションを迅速かつ確実に実現できるよう支援します。」

Silicon Creations社

Pawel Banachowicz氏(PLL Product Line Development Director)

「ケイデンスとの長年のパートナーシップを、Chiplet Spec-to-Partsエコシステムでさらに深められることを嬉しく思います。過去15年間で、当社は主要ファウンドリ向けに100以上のカスタムPLLを開発・提供してきました。これまで高性能・低ジッターPLLや専用クロックソリューションを提供してきたこの協業を、次世代チップレット設計の加速に向けてさらに拡大できることを楽しみにしています。」

Trilinear Technologies社

Carl Ruggiero氏(CEO)

「この画期的な取り組みの一環として、当社の先進的なDisplayPort IPを提供できることを大変嬉しく思います。ケイデンスとの協業により、高性能なビデオ接続を実現し、柔軟で将来対応型のディスプレイソリューションをチップレット・エコシステムに提供します。」

ケイデンスコメント

David Glasco(Vice President of the Compute Solutions Group)

「ケイデンスの新たなチップレット・エコシステムは、チップレット活用の推進における重要なマイルストーンです。マルチダイやチップレットベースのアーキテクチャは、設計の複雑化が進む中で、より高い性能・コスト効率を達成するために不可欠となっています。ケイデンスのチップレットソリューションを用いることで、コスト最適化、カスタマイズ性、構成の自由度を実現できます。幅広いIPポートフォリオとSoC設計の専門知識に、本エコシステムのパートナー企業の事前統合・事前検証済みIPを組み合わせることで、チップレットベースのソリューション開発を加速し、お客様がチップレットを活用した設計目標をスムーズに、確信を持って達成できるよう支援します。」

※本プレスリリースは、2026年1月6日に米国で発表されたプレスリリースを日本語に翻訳したものです。内容および解釈については、英語版が正式なものとされます。

関連リソース

eBook「Helping You Realize Your Chiplet Ambitions」

ウェビナー「Chiplets Solutions: Helping You Realize Your Chiplet Ambitions」

ブログ「Cadence Transforms Chiplet Technology with First Arm-Based System Chiplet」

ブログ「Jumpstarting the Automotive Chiplet Ecosystem」

ケイデンスについて

ケイデンスはAI分野とデジタルツインのマーケットリーダーであり、シリコンからシステムまでのエンジニアリング設計におけてイノベーションを加速させる演算ソフトウェアのアプリケーションのパイオニアです。ケイデンスのIntelligent System Design戦略に基づくケイデンスの設計ソリューションは、ハイパースケールコンピューティング、モバイル通信、自動車、航空宇宙、産業、ライフサイエンス、ロボティクスなど、幅広い市場に対応するチップから電気機械システムまで、世界をリードする半導体およびシステム企業が次世代製品を構築するために不可欠なものです。2024年、ケイデンスはWall Street Journal紙により、世界で最も優れた経営を行っている企業トップ100に選ばれました。ケイデンスのソリューションは無限の可能性を提供します。ケイデンスに関する詳細についてはcadence.comをご参照ください。

この件に関する問い合わせ先

フィールド・マーケティング部

TEL: 045-475-2311 FAX: 045-475-2218

E-mail: japan_pr@cadence.com

すべての画像